FPGA重点知识13条,助你构建完整“逻辑观”之三

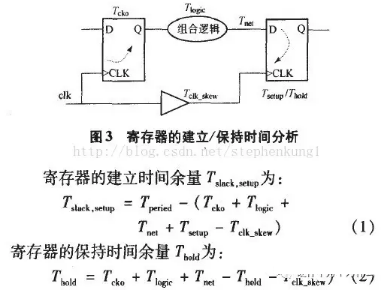

我们的分析从下图开始,下图是常用的静态分析结构图,一开始看不懂公式不要紧,因为我会在后面给以非常简单的解释:

这两个公式是一个非常全面的,准确的关于建立时间和保持时间的公式。其中Tperiod为时钟周期;Tcko为D触发器开始采样瞬间到D触发器采样的数据开始输出的时间;Tlogic为中间的组合逻辑的延时;Tnet为走线的延时;Tsetup为D触发器的建立时间;Tclk_skew为时钟偏移,偏移的原因是因为时钟到达前后两个D触发器的路线不是一样长。

这里我们来做如下转化:

因为对于有意义的时序约束,建立时间余量Tslack,setup和保持时间余量Thold都要大于0才行,所以对于时序约束的要求其实等价于:

Tperiod>Tcko+Tlogic+Tnet+Tsetup-Tclk_skew (1)

Tcko+Tlogic+Tnet>Thold+Tclk_skew (2)

之前说了,这两个公式是最全面的,而实际上,大部分教材没讲这么深,他们对于一些不那么重要的延时没有考虑,所以就导致不同的教材说法不一。这里,为了得到更加简单的理解,我们按照常规,忽略两项Tnet和Tclk_skew。原因在于Tnet通常太小,而Tclk_skew比较不那么初级。简化后如下:

Tperiod>Tcko+Tlogic+Tsetup (3)

Tcko+Tlogic>Thold (4)

简单多了吧!但是你能看出这两个公式的含义吗?其实(3)式比较好理解,意思是数据从第一个触发器采样时刻传到第二个触发器采样时刻,不能超过一个时钟周期啊!假如数据传输超过一个时钟周期,那么就会导致第二个触发器开始采样的时候,想要的数据还没有传过来呢!那么(4)式又如何理解呢?老实说,一般人一眼看不出来。

我们对于(4)式两边同时加上Tsetup,得到(5):

Tcko+Tlogic+Tsetup>Thold+Tsetup (5)

结合(3)式和(5)式,我们得到如下的式子:

Thold+Tsetup <tcko+tlogic+tsetup< p="" (6)

这个式子就是那个可以让我们看出规律的式子。也是可以看出静态时序分析本质的式子。

Tcko+Tlogic+Tsetup是指数据从第一级触发器采样瞬间开始,传输到第二级触发器并被采样的传输延时。我们简称为数据传输延时。下面讲述(6)式两端的含义。

Tcko+Tlogic+Tsetup< Tperiod :约定数据传输延时不能太大,如果太大(超过一个时钟周期),那么第二级触发器就会在采样的时刻发现数据还没有到来。

Thold+Tsetup

综上,我们就可以知道,数据传输延时既不能太大以至于超过一个时钟周期,也不能太小以至于小于触发器采样窗口的宽度。这就是静态时序分析的终极内涵。有了这个,就不需要再记任何公式了。

11、CPLD、FPGA加载原理

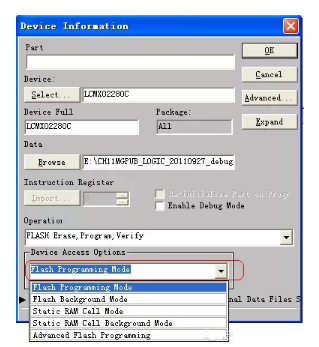

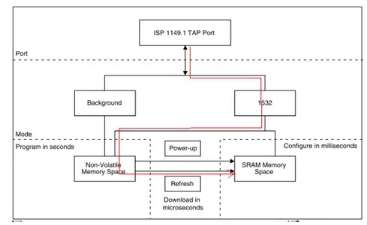

LD一般用JTAG接口进行加载,内部有FLASH和SRAM,CPLD的配置文件可存在在内置的FLASH中,因此下电不会丢失,不需要每次上电的时候,额外对CPLD进行配置结构如下:

方式一:当SRAM为空时(CPLD一次都未加载过或者CPLD内部FLASH存储的配置文件有问题,不能加载到SRAM中),Flash编程进入直接模式,此时CPLD的IO管脚状态由BSCAN registers(边界扫描寄存器)决定,BSCAN registers可以将IO设置成high, low, tristate (default), or current value四种。

方式2:

方式二:当SRAM不为空的时候,Flash 可进行background编程模式.在此模式下,在加载on-chipFlash时,允许CPLD器件仍然维持在用户操作模式下(即CPLD可以正常工作)。

IEEE 1532标准简介IEEE 1532标准是一个基于IEEE 1149.1的在板编程的新标准,标准的名字为IEEE Standard for In-System Configuration of ProgrammableDevices。 在1993年,出现ISP(In-System Programming)的概念和应用。随之产生了应用IEEE1149.1进行ISP的需求。各个厂商提供了类似的不相同的基于JTAG的ISP工具。1996年4月,半导体厂商、ISP工具开发者、ATE开发商正式提出了IEEE 1532标准,旨在为JTAG器件的在板编程提供一系列标准的专门的寄存器和操作指令从而使得在板编程更为容易和高效。IEEE1532完全建立在IEEE1149.1标准之上,在IEEE 1532标准上可以开发通用的编程工具,为测试、编程和系统开发提供规范的接口和器件支持、促进了编程革新,开辟了边界扫描技术新的应用领域。IEEE1532 主要应用在CPLD、FPGA、PROM以及任意的支持IEEE 1532的可编程器件的在板编程。

早期的可编程逻辑器件只有可编程只读存贮器(PROM)、紫外线可按除只读存贮器(EPROM)和电可擦除只读存贮器(EEPROM)三种。由于结构的限制,它们只能完成简单的数字逻辑功能。

其后,出现了一类结构上稍复杂的可编程芯片,即可编程逻辑器件(PLD),它能够完成各种数字逻辑功能。典型的PLD由一个“与”门和一个“或”门阵列组成,而任意一个组合逻辑都可以用“与一或”表达式来描述,所以,PLD能以乘积和的形式完成大量的组合逻辑功能,可以实现速度特性较好的逻辑功能,但其过于简单的结构也使它们只能实现规模较小的电路。

为了弥补这一缺陷,20世纪80年代中期。 Altera和Xilinx分别推出了类似于PAL(可编程阵列逻辑)结构的扩展型 CPLD(ComplexProgrammab1e Logic Dvice)和与标准门阵列类似的FPGA(FieldProgrammable Gate Array),它们都具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点。这两种器件兼容了PLD和通用门阵列GAL(Generic Array Logic)的优点,可实现较大规模的电路,编程也很灵活。与门阵列等其它ASIC(ApplicationSpecific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

12、锁存器、触发器、寄存器和缓冲器的区别

一、锁存器

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。锁存器也称为透明锁存器,指的是不锁存时输出对于输入是透明的。

锁存器(latch):我听过的最多的就是它是电平触发的,呵呵。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。(简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程)。

应用场合:数据有效迟后于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器。

缺点:时序分析较困难。

不要锁存器的原因有二:1、锁存器容易产生毛刺,2、锁存器在ASIC设计中应该说比ff要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和ff来组成锁存器,这样就浪费了资源。

优点:面积小。锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

二、触发器

触发器(Flip-Flop,简写为 FF),也叫双稳态门,又称双稳态触发器。是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发。

触发器(flip-flops)电路相互关联,从而为使用内存芯片和微处理器的数字集成电路(IC)形成逻辑门。它们可用来存储一比特的数据。该数据可表示音序器的状态、计数器的价值、在计算机内存的ASCII字符或任何其他的信息。

有几种不同类型的触发器(flip-flops)电路具有指示器,如T(切换)、S-R(设置/重置)J-K(也可能称为Jack Kilby)和D(延迟)。典型的触发器包括零个、一个或两个输入信号,以及时钟信号和输出信号。一些触发器还包括一个重置当前输出的明确输入信号。第一个电子触发器是在1919年由W.H.Eccles和F.W.Jordan发明的。

触发器(flip-flop)---对脉冲边沿敏感,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变。

T触发器(Toggle Flip-Flop,or Trigger Flip-Flop)设有一个输入和输出,当时钟频率由0转为1时,如果T和Q不相同时,其输出值会是1。输入端T为1的时候,输出端的状态Q发生反转;输入端T为0的时候,输出端的状态Q保持不变。把JK触发器的J和K输入点连接在一起,即构成一个T触发器。

应用场合:时钟有效迟后于数据有效。这意味着数据信号先建立,时钟信号后建立。在CP上升沿时刻打入到寄存器。

三、寄存器

寄存器(register):用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果,它被广泛的用于各类数字系统和计算机中。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。 工程中的寄存器一般按计算机中字节的位数设计,所以一般有8位寄存器、16位寄存器等。

对寄存器中的触发器只要求它们具有置1、置0的功能即可,因而无论是用同步RS结构触发器,还是用主从结构或边沿触发结构的触发器,都可以组成寄存器。一般由D触发器组成,有公共输入/输出使能控制端和时钟,一般把使能控制端作为寄存器电路的选择信号,把时钟控制端作为数据输入控制信号。

寄存器的应用

1. 可以完成数据的并串、串并转换;

2.可以用做显示数据锁存器:许多设备需要显示计数器的记数值,以8421BCD码记数,以七段显示器显示,如果记数速度较高,人眼则无法辨认迅速变化的显示字符。在计数器和译码器之间加入一个锁存器,控制数据的显示时间是常用的方法。

3.用作缓冲器;

4. 组成计数器:移位寄存器可以组成移位型计数器,如环形或扭环形计数器。

四、移位寄存器

移位寄存器:具有移位功能的寄存器称为移位寄存器。

寄存器只有寄存数据或代码的功能。有时为了处理数据,需要将寄存器中的各位数据在移位控制信号作用下,依次向高位或向低位移动1位。移位寄存器按数码移动方向分类有左移,右移,可控制双向(可逆)移位寄存器;按数据输入端、输出方式分类有串行和并行之分。除了D边沿触发器构成移位寄存器外,还可以用诸如JK等触发器构成移位寄存器。

五、总线收发器/缓冲器

缓冲寄存器:又称缓冲器缓冲器(buffer):多用在总线上,提高驱动能力、隔离前后级,缓冲器多半有三态输出功能。当负载不具有非选通输出为高阻特性时,将起到隔离作用;当总线的驱动能力不够驱动负载时,将起到驱动作用。由于缓冲器接在数据总线上,故必须具有三态输出功能。

它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。

Buffer:缓冲区,一个用于在初速度不同步的设备或者优先级不同的设备之间传输数据的区域。通过缓冲区,可以使进程之间的相互等待变少,从而使从速度慢的设备读入数据时,速度快的设备的操作进程不发生间断。

缓冲器主要是计算机领域的称呼。具体实现上,缓冲器有用锁存器结构的电路来实现,也有用不带锁存结构的电路来实现。一般来说,当收发数据双方的工作速度匹配时,这里的缓冲器可以用不带锁存结构的电路来实现;而当收发数据双方的工作速度不匹配时,就要用带锁存结构的电路来实现了(否则会出现数据丢失)。

缓冲器在数字系统中用途很多:

(1)如果器件带负载能力有限,可加一级带驱动器的缓冲器;

(2)前后级间逻辑电平不同,可用电平转换器加以匹配;

(3)逻辑极性不同或需要将单性变量转换为互补变量时,加带反相缓冲器;(4)需要将缓变信号变为边沿陡峭信号时,加带施密特电路的缓冲器

(5)数据传输和处理中不同装置间温度和时间不同时,加一级缓冲器进行弥补等等。

评论