工程师经验谈:合适的FPGA电源的选择

现场可编程门阵列(FPGA)是可以包括数千个典型的、可编程逻辑单元,一个由线和可编程开关的矩阵与单独的逻辑单元互连,典型的设计包括指定每个单元的简单逻辑功能和选择性地关闭互连矩阵中的开关。

本文引用地址:http://www.eepw.com.cn/article/201710/366725.htmFPGA主要用于原型IC系统,当设计完成后,设计人员可以将逻辑转换为以更高速度工作的硬连接线IC,为了能正常工作,FPGA必须采用适当的电源管理技术。

为现场可编程门阵列 (FPGA) 设计电源系统可不是件容易的工作。FPGA是高度可配置的半导体器件,这种器件在大量应用和终端市场中使用。常见示例包括通信、汽车、工业、医疗、视频和国防等应用。由于它们的高度可配置性,可以在它们周围放置不同的组件,形成最终系统设计。虽然可能会有数不尽的应用和系统,但是所有设计的一个共同特性就是它们全都需要电源。

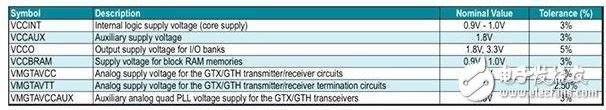

通常需要几个电压轨为FPGA供电。根据应用的不同,主输入电源可以采用背板电源、隔离电源、非隔离电源,甚至是电池供电的方式。这些主输入通常生成一个中间DC电压来为FPGA的主电压轨供电。这些中间电压通常为5V或12V的DC电压。表1和表2中列出了FPGA的某些典型电压轨、电压和容限值。

表2:Virtex 7FPGA的电源要求。

表2:Zynq 7000系列片上系统 (SoC) 的电源要求。

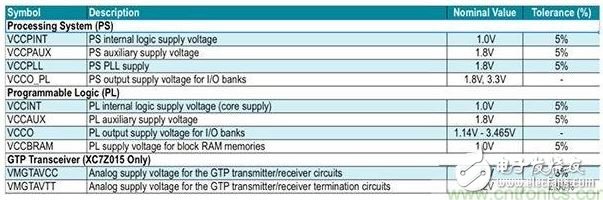

为每个电压轨确定合适的电流电平是一件比较棘手的工作,原因在于电流的范围可以从几百毫安到60A,甚至更高。如果事先进行规划的话,情况就会完全不同,事先规划可以避免对电源轨的过度设计,从而避免花费太多,或者避免设计不充份,从而导致必须推倒重来等错误。FPGA销售商提供准确的工具,这款工具根据客户对FPGA的使用方式来估算出最差情况下的功耗。

图1中显示的Xilinx功率估算器 (XPE),涵盖了数个Xilinx FPGA系列。借助于这款工具,客户可以选择正在使用的部件,并且输入时钟和配置信息,来确定电源需求,并且根据估算值来选择合适的器件。

图1:功率估算器工具。

设计注意事项

在选择一款符合FPGA应用需要的电源时,必须将很多因素考虑在内。成本、尺寸,以及效率,始终是电源设计过程中需要注意的因素。不过,在FPGA 应用中,某些电源轨将会有不同的要求。内核电源轨通常需要在线路、负载和温度范围内保持更加严格的精度。某些电源轨,比如说收发器,对于噪声更加敏感,并且需要将它们的输出保持在特定的噪声阀值以下。还需注意的是,某些具有共模电压的电源轨可组合在一起,并且可以用一个铁氧体磁珠进行隔离,以实现滤波或作为一个负载开关。

当进行符合容限要求方面的设计时,需要将全部的固定和动态运行条件考虑在内。首先,选择一款基准精度少于1%的稳压器,这为客户预留了最大的设计裕量空间来处理负载瞬变等动态运行条件。

在设计高速收发器电源轨时还需谨慎,因为这些灵敏电源轨上的噪声会使性能下降,并且增加抖动。低压降稳压器 (LDO) 是这些电源轨的理想选择。不过,当需要更高电流时,只要输出纹波的典型值在10kHz至80MHz频率范围内保持在10mVpk-pk以下,就可以使用开关电源。专用FPGA数据表将包含与收发器需求相关的详细技术规格。

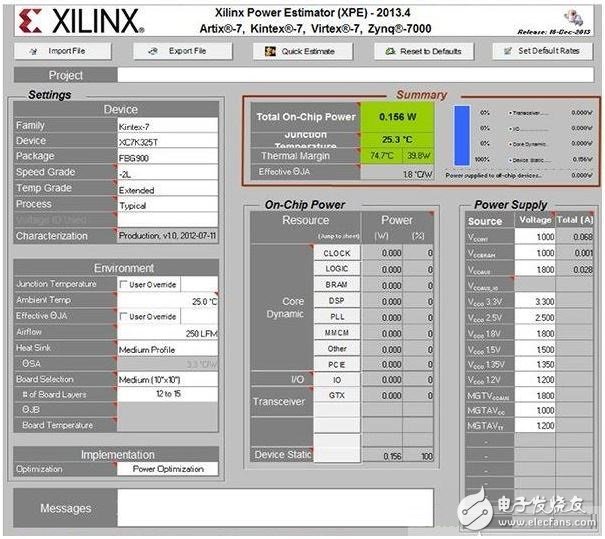

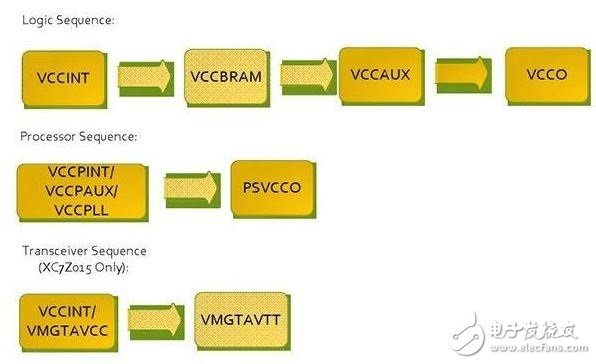

电源排序是FPGA电源设计时的另外一个重要方面。由于有数个电源轨为FPGA供电,下面推荐的电源序列在启动时汲取最小电流,这反过来防止了对器件的损坏。图2中显示的是针对Virtex 7系列FPGA上的逻辑电路和收发器电源轨的建议加电电源序列。针对Zynq 7000系列SoC的处理器排序显示在图2中。

图2:针对Virtex 7 FPGA的推荐加电序列。*VCCINT and VMGTAVCC可同时加电,只要它们在VMGTAVTT之前启动,它们的加电顺序可以互换。

图3:建议用于Zynq 7000系列SoC的加电序列。

对于Xilinx 7/Zynq 7000系列器件来说,这些电源轨必须具有一个单调上升,并且必须在0.2ms至50ms的周期范围内加电,而对于Xilinx Ultrascale FPGA系列器件来说,这个周期范围在0.2ms到40ms之间。建议断电序列与加电序列的顺序相反。

电源解决方案

一旦已经估算出合适的电流电平,并且全部设计注意事项已知的话,电源设计人员可以开始器件选型。有几个选项可供选择,诸如低压降稳压器 (LDO)、开关模式电源 (SMPS) 和集成模块,它们都具有不同的优缺点。例如,由于其简单性和低输出噪声,LDO是某些较低电流FPGA电源轨的理想选择。而LDO的缺点在于,它们的效率不高,并且会在较高电流时,通过导通晶体管大量散热。它们通常适用于那些功率较低的应用,以及那些要求低噪声的应用。

当需要的电流值大于2安培,并且效率更为重要的话,设计人员可以选择开关模式电源 (SMPS)。这些器件在单相位配置中的效率可以达到90%以上,并且提供高达30A的电流。与LDO相比,它们的设计工作量更大,并且在较轻负载时的效率不太高,不过它们更加灵活,并且在较高电流电平时的效率较高。

电源模块,比如说LMZ31506易电源 (simple switcher),可以将一个DC/DC转换器、功率金属氧化物场效应晶体管 (MOSFET)、一个屏蔽电感器,和无源组件集成在一个薄型四方扁平无引线 (QFN) 封装内。由于全部组件已经集成在一个封装内,并且仅需最少的外部组件,这样可以减少设计时间。

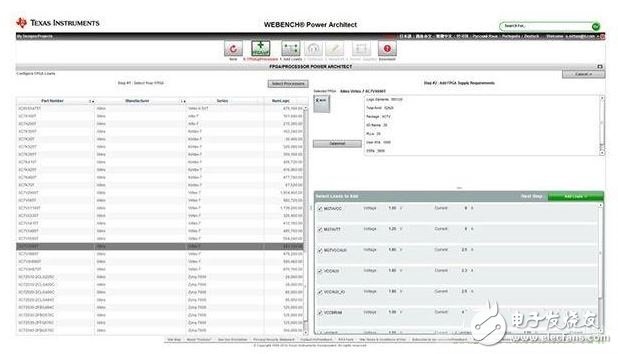

Webench FPGA架构设计工具

Webench FPGA架构设计工具(图4)是一款十分有用的工具,能够帮助电源设计人员在几分钟内构建数个FPGA电源轨。这个工具包含某些最近上市的FPGA的详细电源需求。在这款工具中,你只需选择正在使用的FPGA,并且将电流调整到需要的水平上,而这款工具将形成一份综合性的设计报告。

图4:Webench FPGA架构设计工具。

评论