在FPGA开发中尽量避免全局复位的使用?(1)

最近几天读了Xilinx网站上一个很有意思的白皮书(white paper,wp272.pdf),名字叫《Get Smart About Reset:Think Local, Not Global》,在此分享一下心得,包括以前设计中很少注意到的一些细节。

在数字系统设计中,我们传统上都认为,应该对所有的触发器设置一个主复位,这样将大大方便后续的测试工作。所以,在所有的程序中,我往往都在端口定义中使用同一个reset信号(其实好多时候根本就没有用到)。所以,当看到文档中提到,“不建议在FPGA设计中使用全局复位,或者说应该努力避免这种设计方式”时,许多设计人员(包括我)都会觉得非常难以理解,这种设计思想跟我们通常的认识是相冲突的!

继续读下去,不知不觉发现这个白皮书讲的还真是在理。接下来把我的个人理解讲述一下。

1.全局复位是不是关键时序?

全局复位信号一般由以下三种途径获得:

1. 第一种,最常见的,就是用一个复位按钮产生一个复位信号接到FPGA的全局复位管脚上。它的速度显然是非常慢的(因为是机械结构),而且存在抖动的问题。

2. 第二种是上电的时候由电源芯片产生的,如TI的TPS76x系列的电源系统一般都可以产生复位信号,供主芯片上电复位使用。

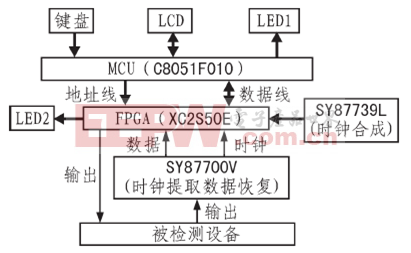

3. 第三种是由控制芯片产生的复位脉冲,这个是我们设计人员可以方便使用程序控制的。

在这些情况下,复位信号的变化与FGPA芯片内部信号相比看起来是及其缓慢的,例如,复位按钮产生的复位信号的周期至少是在毫秒级别的,而我们FPGA内部信号往往是纳米或者微秒级别的。复位信号的频率是如此之低,以至于我们任务它不属于关键时序(not TIming-criTIcal)。即使是对此类信号进行时序约束,约束的周期也是非常长的。全局复位脉冲的周期远大于时钟周期,所以传统意义上假设FPGA芯片中所有的触发器都能够得到有效的复位。

然而,随着FPGA性能和工作频率的快速提高,这种假设开始不再成立。此时,全局复位信号的产生开始成为时序关键的问题。

评论