【E课堂】芯片反向设计流程

电路整理

本文引用地址:http://www.eepw.com.cn/article/201707/361304.htm在版图提取完毕之后,下一个步骤就是电路整理。提取完的电路图是混乱的,没有层次关系。那么如何将其整理成具有层次关系,让人一看就懂呢?

1、这就涉及到有关芯片的一些常识了。芯片分为数字芯片和模拟芯片,但是数字芯片必定会包含模拟电路,而模拟芯片却可以不包含数字电路。它们有如下一般特征:

A、数字芯片,必有时钟振荡电路、复位电路这些模拟电路。必有寄存器,而且整个数字部分最耗面积的部分往往都是寄存器。寄存器的使用量是很大的,因此,在版图上呈现的就是有大数量的图像一模一样的电路,这种电路往往都是寄存器。

B、模拟芯片,有带隙基准电路。

2、说完了芯片版图常识,另外一个重要的有助于理解所提取的电路的工具就是待反向的芯片的数据手册!这是最重要的,我们所有有关于芯片的信息都是从数据手册上得来的。所以一定要善用DATASHEET!在芯片数据手册上,一般会对芯片的功能进行说明,对芯片如何运行进行说明,这些说明将有助于我们对于电路的整理。

比如说,芯片手册上说道用了I2C,那么电路中肯定有一大块电路是属于I2C的。一般来说,版图的布局都是将同属于一种功能的管子会集中放置在一起。I2C电路的特征,从I2C协议的原理上可以知道,它就两根信号线,一根时钟,另一根数据线。数据在芯片内部一般是并行传输比较方便,所以,I2C电路一定会有串并转换电路,而串并转换电路一般是寄存器,而且一般是8位。根据这个推断结果,就在提取的电路中去寻找8个在一起的寄存器,它们其中一组就是I2C电路的一部分,再根据芯片版图的I2C PAD位去寻找,看连接到了那一组寄存器上,那么整个I2C的电路就被识别出来了。因此:

a、靠着芯片手册对芯片功能的说明,

b、加上芯片的一些常识性知识,

c、加个人的这种对电路原理的推理,就可以相对较快的将电路分层次的整理出来。

逐步的理解整个芯片的原理。当然,由于芯片电路的庞大的关系,有时候电路并不是需要完全理清楚,对于不那么重要的电路可以不理会。只要保证连接关系没连接错就行。这阶段,只会用到cadence ic5141的virtuoso schematic软件。

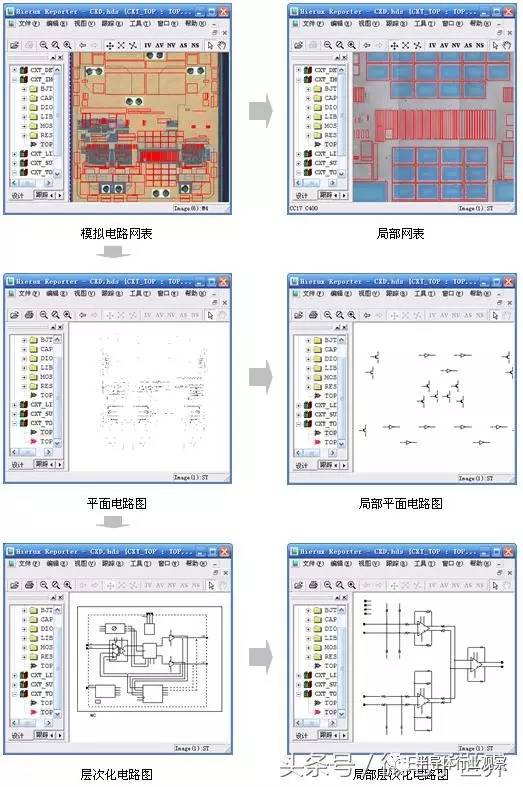

芯片电路整理

电路仿真及修改

电路整理好了,下一步就是进行电路的仿真及修改了,根据工艺选择步骤选择的工艺来进行。先说明一下这阶段所使用的工具:

1、cadence spectre,一般集成在cadence ic5141里面,是模拟电路仿真工具(ps:最原始的版本是集成在IC5141内部,但功能不全,所以需要单独安装新版本,软件名为MMSIM61,随着版本的升级,它的名字也在修改),当然,数字电路也可以进行仿真,数字电路的本质还是模拟电路;

2、synopsys公司的 Hspice,与spectre一样的仿真工具,另有些差别。

3、Mentor公司的 Modelsim,主要在windows上使用,用于verilog网表的仿真。

模拟电路仿真工作流程:在cadence中搭建好仿真环境,设置好仿真参数,选用spectre或者hspice,然后就可以进行仿真的。另外,也可以将电路导出成CDL网表,拷贝到Windows上,用Windows版本的Hspice进行仿真,这样做的优点是Windows易于操作。另外说明一下spectre和hspice的一项区别。spectre仿真的时候会保存所有电路节点的数据,这样做优点是方便查看各个节点的数据,缺点是仿真消耗的时间太长,保存的数据文件太大,这一点在遇到大型电路的时候会很耗时(不知道最新版本改进这一点没有,鄙人没有用过最新版的spectre)。hspice仿真之前可以自己选定所要查看的节点,这样做就可以减少仿真时间和减小数据文件的大小。

数字电路仿真工作流程:在virtuoso schematic中将整理好的电路路中数字电路部分导出成网表文件,再拷贝到windows系统上进行仿真。windows系统上数字电路网表的仿真采用Modelsim。(这么做的原因是linux系统不太方便)使用Modelsim仿真,最重要的是写好testbench(貌似这句是废话)。

关于电路的修改,这部分其实不好总结,因为每一款芯片都有不同的参数,所要修改的地方都不太一样,我所知道的是,必定要考虑修改的地方往往都是有关模拟电路的,例如,时钟振荡、复位电路、开漏输出管、带隙等,修改的目的是为了与当前所选用的工艺适配,以满足芯片datasheet的参数要求。另外,数字部分的电路其实一般来说是不需要修改的,但有时为了节省版图面积,会缩小寄存器管子的尺寸,毕竟缩小一个,就等于缩小了几十个。这一阶段其实是一个不断的迭代过程,它要和版图绘制结合起来,这样才能够保证芯片功能和性能的完整。

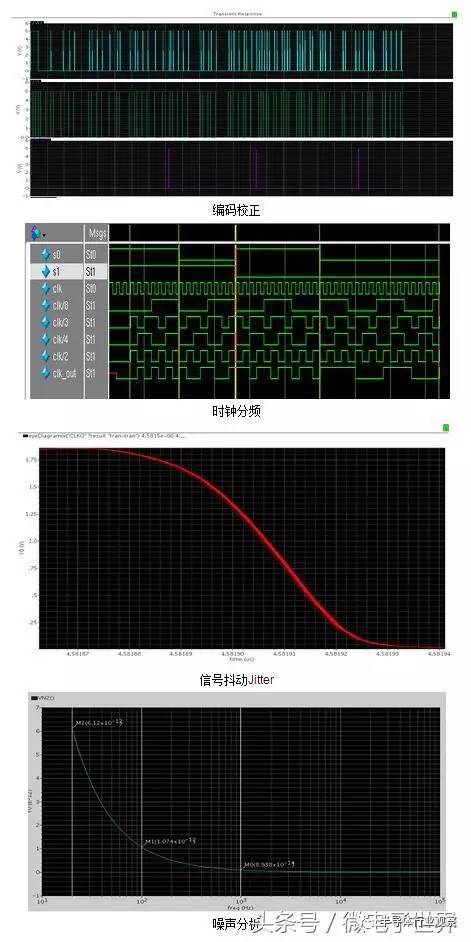

电路仿真

版图绘制

这部分在电路整理完之后就可以开始进行了,并配合电路仿真与修改,逐步晚上版图的绘制。该阶段所使用的主要工具有 1、cadence ic5141的版图绘制软件;2、cadence Dracula Diva或者Calibre,这两个用于版图DRC(设计规则检查)、LVS(版图一致性检查);一般而言,calibre会更加常用一些,毕竟这可是Mentor公司的招牌软件之一。在版图绘制好并进行各种检查无误之后,就可以tapeout,准备流片了。

评论