CPLD MAX II低成本架构

在高密度应用环境下,基于查找表(LUT)的LAB和行、列布线模式具有更高的裸片尺寸/成本效率。由于MAX II CPLD基于LUT架构,达到了降低成本的目的,结合其即用性、非易失性和可再编程特性,使MAX II 系列成为有史以来成本最低的CPLD。

注释:

随着LAB数量的增加,布线资源指数性的增长,使得布线资源主导裸片面积

随着LAB数量的增加,布线线形增长,获得高效的裸片面积

低成本设计

MAX II器件的构造采用了低成本设计方法,首先它选择了一种流行的低成本的封装。通过使用限制焊盘面积的,错列I/O焊盘方案,获得单个I/O成本最低的管脚方案,从而实现最小的裸片尺寸。其次,该器件在I/O引脚所包围的环内组装了最大数量的LE。这种基于LUT的架构在I/O约束的最小的空间内获得了最大可能的逻辑容量。

MAX II架构

突破性的新型MAX II CPLD架构包括基于LUT的LAB阵列、非易失性FLASH存储器块和JTAG控制电路(见图2)。多轨道连线设计采用了最有效的,直接将逻辑输入连接到输出的连线,从而获得了最高的性能、最低的功耗。更多关于MAX II架构的详细信息可参见MAX II器件系列数据手册。

与QuartusII软件设计一致性

为简化设计优化过程,MAX II器件架构和Quartus® II软件装配算法保持精确的一致性,在管脚锁定时优化tPD、tCO、tSU和fMAX性能。当设计的功能改变时,Quartus II软件采用管脚锁定约束和按钮式编译流程,提高了满足或超过性能要求的能力。免费的Quartus II基础版软件支持所有MAX II器件。

电压灵活性

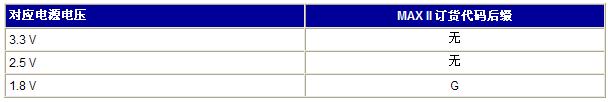

MAX II架构支持MultiVolt™内核,该内核允许器件在1.8V、2.5V或3.3V电源电压环境下工作。目前对应电源电压有两个器件系列可选(见表1和图3)。该特性使设计者得以减少电源电压种类数量,简化板级设计。

图3. MultiVolt内核操作

注释:

VCCINT = 1.8 V 旁路调节器

MAX II器件还支持Altera的多电压I/O 接口特性,允许和其他器件保持1.5V、1.8V、2.5V或3.3V逻辑级的无缝连接(见图4)。EPM240和EPM570器件含两个I/O区,EPM1270和EPM2210含4个I/O区,每个I/O区可以采用独立的VCCIO供电。

图4. 多电压I/O能力

评论