针对微控制器应用的FPGA实现

在选择微控制器时应考虑哪些因素?本文将主要探讨采用FPGA的嵌入式应用。不过,选择任何微控制器的标准本质上都是相同的。设计者需要考虑下列因素:终端产品的成本是多少?实现设计以及存储控制程序需要多少内存?对输入输出的要求?对寄存器的要求?如何与其它器件集成?

传统的MCU已作为一种非定制的特殊应用标准产品(ASSP)上市,每个供应商都提供了不同的功能以实现差异化并迎合市场的各种需求。将FPGA与MCU IP结合可提供比传统MCU更加灵活的硬件平台,并有助于实现前面列出的各项考虑因素。

虽然FPGA比单片MCU昂贵,但其附加的功能(如嵌入式DSP、存储块以及灵活的I/O环)可以抵消多个器件的成本;FPGA提供了更加灵活的存储结构,一旦数据和指令需要改变,则用户可以调整硬件设计来与之匹配;现代系统中有各种各样的信号标准和接口协议,因此对输入输出的要求非常严格,具有可编程片上缓冲器的FPGA在这个领域具有独特优势。例如,Lattice MachXO器件可在各种电平下支持单端LVCMOS/LVTTL和差分LVDS/LVPECL。就寄存器和暂存存储器资源而言,面向FPGA的MCU IP核所提供的灵活性可改变配置以满足应用的需求;FPGA是解决器件集成问题的理想方案。可编程查找表(LUT)、寄存器和存储器提供了额外的集成功能,同时灵活的可编程I/O和专用接口(如双数据速率(DDR))使其与多个器件的握手更加容易。

对于许多微控制器应用来说,FPGA是非常理想的器件,因为其成本相对低廉,包含大量的嵌入式存储块,具有足够的I/O以应对几乎所有控制器功能,拥有丰富的寄存器,并支持包括LVCMOS、SSTL及差分LVDS信号传输在内的许多I/O标准。

基于闪存的非易失性FPGA

FPGA的制造工艺有多种,包括一次性编程(反熔丝)、易失性(基于SRAM),以及使用基于EE或闪存的非易失性工艺。

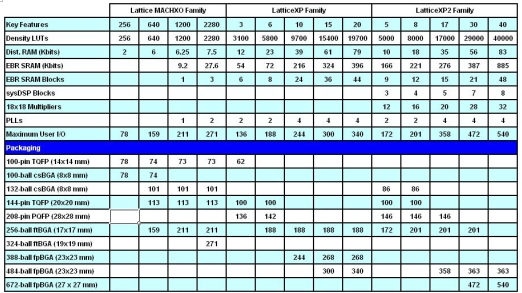

表1列出了器件密度、封装类型、可用I/O数、嵌入式和分布式存储器,以及PLL和嵌入式DSP块。例如,基于闪存的FPGA采用130nm和90nm工艺。广泛的选择范围使得找出满足特殊微控制器应用需求的器件更容易一些。

微控制器应用实例

FPGA的灵活性使其适用于许多微控制器应用,以及包含微控制器的更复杂的设计。

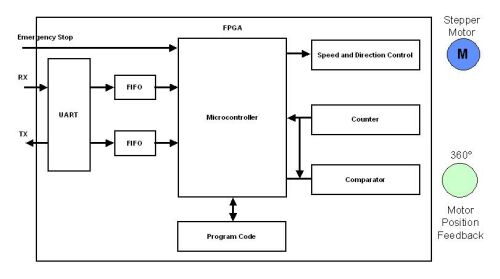

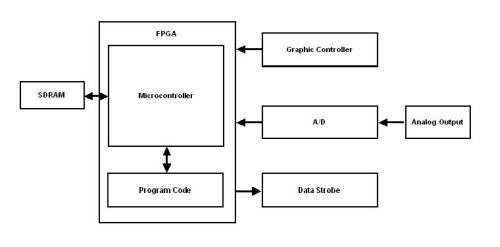

像家用电子设备、工业机器人以及正在增长的新兴汽车应用(从GPS、引擎控制到制动系统)这些产品都包括图1、2和3中所示的微控制器。

在马达控制应用中,系统发送和接收来自微控制器的信息,以调整步进电机的速度和方向。来自系统的输入告知微控制器增大或减小马达和控制器的速度,微控制器再依次告知系统马达的实时速度和方向。

导航系统采用微控制器调整系统的图像显示器,根据微控制器的输入提高或降低分辨率。

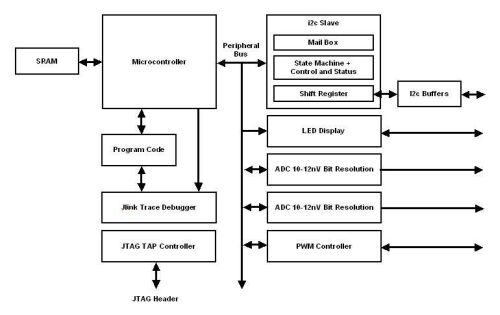

图3中的设计展示了一个片上系统的实现,包括微控制器、外围总线和几种外设功能,以及用于显示寄存器文档、暂存存储器、调用栈、程序计数器、标记和跟踪列表的硬件跟踪调试器。同时还支持微控制器的单步、多步和断点功能。

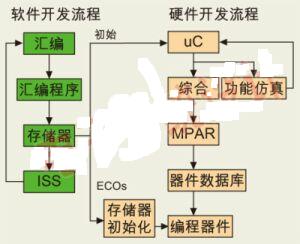

片上系统的例子可用来说明设计工具流程和实现(图4)。

微控制器工具和实现

FPGA微控制器的高效率和紧凑实现使得2280 LUT MachXO器件可用于说明图3中片上系统的设计。

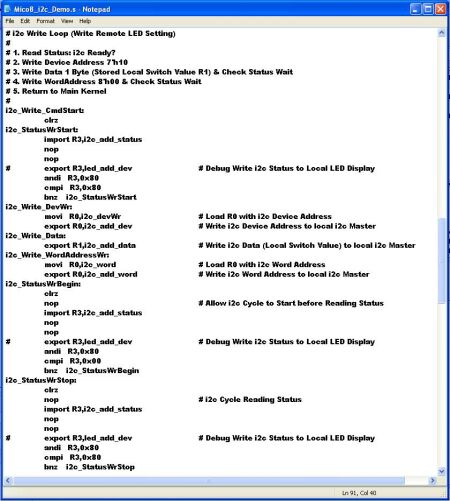

启动该设计的最简单方法是参考“快速启动指南”或项目向导一步一步地设计FPGA。一旦设计项目创建好,下一步就是编写微控制器程序。C或汇编语言是目前最流行的MCU编程语言。图5显示了用汇编语言编写的I2C Slave程序块。

必须对微控制器的每个单元进行分析以决定要执行的操作。如代码实例所示,I2C写循环具有5种操作:读状态、写器件地址、写数据、写字地址及返回。请注意代码都加上了注释。

虽然汇编语言的规范在各种MCU上大多是一致的,但设计者还是应该查阅供应商的MCU指令集文档,以了解哪些操作是得到支持的。将汇编源代码转换到ROM初始化文件的汇编程序是由命令行驱动的,和指令集仿真器一样,这可以通过汇编器供应商工具套件获得或者从网上下载。其中有些工具是作为开放源代码工具提供。例如,LatticeMico8微控制器IP(知识产权)就是作为开放源代码提供,这是实现嵌入式微控制器的一种独特有效途径,可使用户拥有最大的灵活性。

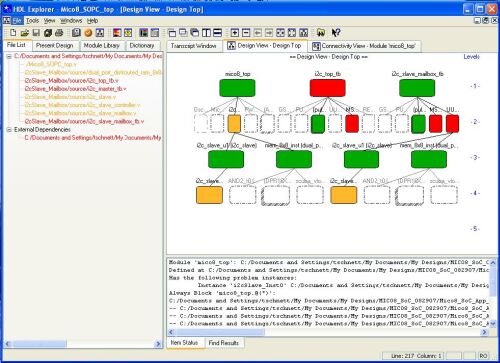

HDL调试和设计规则检查

嵌入式微控制器IP可以描述整个设计,或者作为一个大型设计的一部分与附加代码结合在一起。寻找一种有助于设计HDL调试和规则检查的工具是非常明智的。这种工具会生成该设计的分层结构和互连性的图形表示。用户可以通过各种图形和分层结构来观察设计,并利用智能工具交互探测视图以发现各种问题。

这对于IP集成的维护和复杂FPGA HDL设计的重设计都是很有用的,IP集成需要全面深入的途径进行设计分析和管理。相比传统仿真器或综合工具,这种工具可以实现设计结构的更高层抽象。这有助于创建并管理文档以及分析设计结构,从而极大地减少了花费在这些项目上的设计时间。

功能仿真

功能仿真首先创建一个工作库,设计被编译到该工作库中。仿真器通过图形用户接口、菜单或命令行使该过程更加顺利。这其中包含了设计文档和测试向量(test bench)。测试向量实例化该设计,并将数据加载到输入端。当运行设计时,测试向量被应用于该设计并显示结果(通常以波形的形式)进行分析。

可利用各种仿真器实现设计的功能仿真。如果已对整个系统建模,则可以在系统级进行功能仿真,或者对单个设计单元进行仿真以确保正确的语法和功能已在RTL级建模。在这种特殊情况下,有两家OEM的仿真器可供选择。Aldec公司的Active-HDL Lattice Designer Edition Lite是一种附加的仿真环境。它不但提供混合语言VHDL和Verilog仿真,还可提供面向FPGA设计的可选设计流程。另一种选择是Mentor Graphics的ModelSim,它能够提供VHDL和Verilog语言以及门级时序仿真,以对设计进行完整的仿真和分析。

综合

一旦完成功能仿真,下一步就是综合。综合可以用独立的方式完成,或者在供应商的项目导航工具中作为后台函数运行。综合获取设计、进行逻辑优化并实现工艺映射。独立模式综合的步骤包括建立项目、加入源文件、设置约束、运行设计和分析结果。约束是综合的实现选项,例如扇出限制、使用全局置位/复位。属性则附属于对象,以控制其依附的特定对象的优化、映射和分析。目前可提供两种领先的综合工具。

Precision RTL综合工具是Mentor Graphics公司的重要RTL综合解决方案。利用Precision RTL界面可以很容易地获取有用的特性和工具,例如示意图(RTL/工艺)观察器、约束分析器、PreciseTime(用于高级时序分析)、支持时序调整(re-timing)等等。这些高级工具有助于改进效率并最终优化结果。

Synplicity公司的Synplify综合工具是一款高性能、复杂的逻辑综合引擎,它利用专有的行为提取综合技术(Behavior Extracting Synthesis Technology)提供快速、高效的FPGA和CPLD设计。简单的用户接口和强大的综合引擎结合在一起能迅速提供优化的结果。

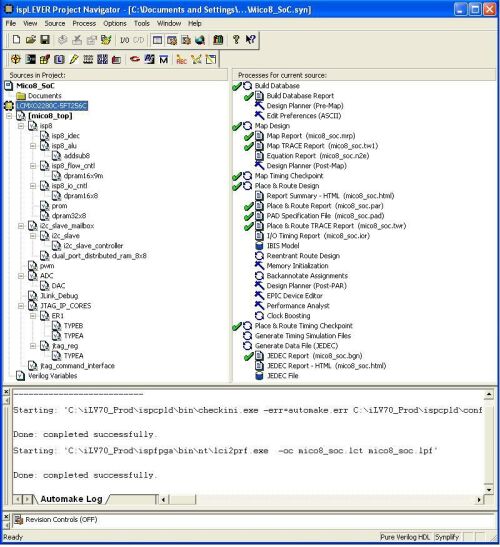

设计实现

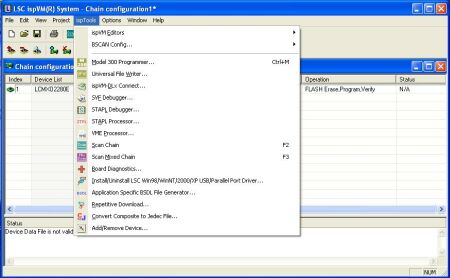

面向映射、布局和布线(MPAR)的设计实现是利用供应商的工具套件完成。这一工具套件包含用于建立项目的项目导航器(Project Navigator),以及任何FPGA设计所必需的其它工具。在这种情况下,源文件被放置在左边的窗口,项目处理在右边的窗口进行,但所有的窗口都是可停靠的,以便用户定制任何视图。Log窗口记录所有的处理,并列出在处理过程中产生的全部警告和错误信息。用户可以通过下拉菜单或者工具栏中的图标使用各种工具。图7为Lattice公司ispLEVER工具套件中的Project Navigator。

实现工具(如Design Planner)可提供I/O和引脚设置、物理和逻辑视图以及平面布局。TCL/TK脚本可以运行多次迭代以优化设计。Project Navigator中包含了静态时序、逻辑调试和功率计算工具。

编程软件

设计完成后,通过如图8所示的编程软件对硬件进行编程。这个工具将提供直观的用户界面GUI,可自动对系统主板进行扫描,选择必需的编程文件并执行合适的编程算法。通过供应商提供的SVF文件,该工具支持符合IEEE 1149.1标准的器件编程。对于大多数系统内可编程器件来说,该工具还可以生成IEEE 1532 ISC数据文件。

调试接口

一旦实现了硬件,设计者将主要关注运行在嵌入式系统上的软件。ISS可用来确定原型功能以及评估对存储器资源的需求。当硬件集成、端口连接以及查找错误均完成之后,通常不需要再更改代码。

在嵌入式系统的FPGA设计流程中,采用汇编器对更改的程序进行再编译,以建立FPGA片上指令或数据存储配置的新存储映像。然后通过一个简单的ECO将映像再次映射至FPGA的存储块。这样设计者就能跳过耗时的综合以及设计流程的布局布线阶段。存储器初始化工具将利用汇编器创建的新型16进制或者2进制映像重写存储器配置。

一旦post-PAR数据库被修改,则只需通过新的编程位流或者JEDEC对FPGA进行再编程。

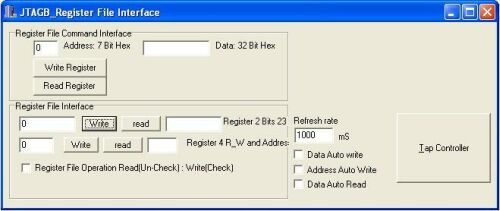

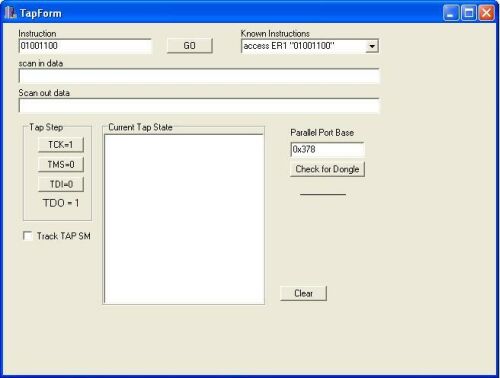

能够控制内部寄存器以及在设计调试阶段实现寻址是非常有用的。为达到这一目标,OrCAstra或JLINK接口等工具(如图9和图10所示)提供了功能强大、易于使用的方法。

本文小结

对于FPGA中的嵌入式微控制器设计而言,一个完整的系统设计需要一批强大的工具。本文中的例子采用了独特的开放源代码微控制器汇编器和指令集仿真工具。领先的第三方厂商可提供综合和仿真工具。用于创建和优化设计的重要实现工具,以及有效的编程和设计调试形成了这一综合设计套件,它是设计获得成功的关键。

评论