基于CPLD的电子秤逻辑接口设计

现代电子仪器系统的多功能化、智能化程度不断增加,并且随着实际应用场合的改变,随时都有可能要求对系统功能进行升级,因此在硬件设计上越来越要依靠EDA辅助设计手段。本文主要讨论了基于CPLD的电子秤逻辑控制电路设计,重点介绍CPU地址空间扩展问题,解决了热敏打印机驱动设计及其他接口设计问题。

1 系统组成及设计指标

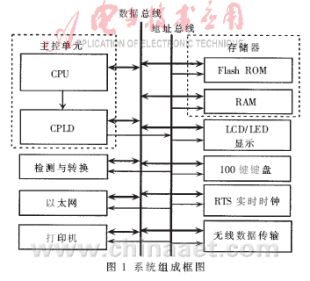

本文所设计的电子秤系统包括主控单元、存储器、键盘显示、检测与转换、数据传输与通信、打印以及系统时钟等硬件模块,图1所示为系统组成框图。由于采用了CPU和CPLD协同控制的设计方案,硬件模块间的关联性高,电路元器件数量少,对系统EMC有明显改善,更为重要的是符合嵌入式软件的设计理念,对系统实时操作系统的移植、管理大有裨益。它除了计量、打印等一般功能外,还具备良好的用户/客户LCD中文图形人机接口界面、以太网远程控制与数据传输、C-S无线数据传输等功能,操作简单直观,扩展、升级更新迅速方便,在不改变控制系统的前提下,更改CPU方案也很方便,如改成DSP/ARM方案。

系统功能与设计指标为:最小称重5g;2MB Flash存储器,128KB带电电池保护RAM;128×64点阵LCD显示界面,100键键盘,46位客户LED;10MHz以太网通信接口;905MHz智能信道扫描无线通信接口;精工高速热敏打印机等。

2 主控单元

主控单元的功能是控制整个电子秤系统的运行状态、协调各个功能模块的关系以及处理过程信息等,主要包括改进型51核单片机和CPLD两部分。

采用单片机作为主控CPU主要是从产品成本考虑的。很多新型MSC51核单片机不但软件、硬件与传统的MCS51系列单片机完全兼容,并且在速度、抗干扰性能、稳定性以及性价比等方面较后者具有明显优势。图2中CPU采用SST89E58,它与8位标准51系列单片机完全兼容,工作频率0~40MHz,工作电压范围2.7V~5.5V,其Super Flash存储结构等先进特性可以为用户提供极高的可靠性和极低的成本。该单片机与CPLD结合,可以建立功能强大的商用电子秤操作、控制平台。

商用电子秤的性能要求决定了硬件设计的复杂性。本文用CPLD搭建了可重构数字平台作为逻辑控制部件,所有时序控制、地址分配全部交给CPLD完成,用来代替传统的低密度AISC器件,充分发挥CPLD的优势,使CPU对外接器件近似透明,从而可以专注于过程信息的处理,不过多参与硬件控制。图2中CPLD采用1片Altera公司MAX7000系列CPLD EPM7256AET144-7,该芯片有144个引脚,能够解决包括存储器访问、键盘扫描、显示等功能模块的控制和驱动问题,用单片器件实现了CPU与所有外围设备的逻辑接口,使得整个操作控制系统的主板面积大为缩减,整体性能稳定性大为提高。在CPLD中实现的功能模块有:地址译码、打印机驱动、PWM调制转换等部分。为提高开发效率,减少调试中的不可预测问题,采用分级、分步骤设计方法,设计一部分,调试一部分。

3 接口逻辑与地址分配

商用电子秤的应用环境决定了它所需要的外扩端口资源多、存储器容量较大,因此在逻辑设计中,地址分配与管理问题就显得特别重要。

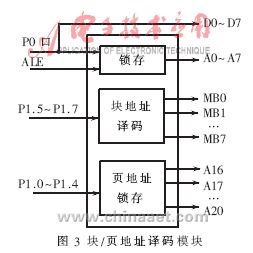

首先,由于单片机64KB的寻址范围无法覆盖2MB存储空间,本文采用了分块-分页的方法管理存储器:将P1与P2/P0口一起作为地址线使用,使总的地址线达到24条,CPU的有效寻址空间高达16MB单元。同时,这16MB空间被进一步平均划分成8个块,每块分32页,每页64KB。其中P1.5-P1.7线作为块寻址线,分别供Flash、RAM、I/O口使用;P1.0-1.4线作为页寻址线,刚好生成32个有效页地址;P2/P0作为单片机默认的地址总线,用来寻址每页内连续的64KB存储单元。寻址实现方法:每寻址一个单元,单片机分两次送出地址号,第1次从P1口送出块/页地址号,第2次从P2/P0口送出页内地址号。块地址不能直接送给目标器件,而是经过CPLD译码后送给对应器件,如图3所示。显然,P0口仍旧复用为数据总线和低8位地址总线,P0口数据经过CPLD锁存后作为低8位地址给存储器使用,而P0口直接引出的数据线并接到所有器件的数据线上。CPU工作于40MHz时钟频率,中和每次寻址送两次地址对速度带来的影响。

其次,由于单片机的P1口已被扩展为地址线,而P3口又只能用其第二功能,故已再无其他端口线可以用作通用I/O控制线。为此,本文采用I/O口统一寻址方式,除了存储器以外的器件全部安排在I/O寻址空间,所有数据(包括串行通信中的串-并转换结果)都经过CPLD缓存之后再送入CPU中,所有存储器及外部I/O端口统一分配地址:第1块A00000H~BFFFFH地址分配给FLASH使用,第2块C00000H~C1FFFFH地址分配给RAM使用,第3块分配给其他并接在I/O总线上的所有端口使用。存储器组织结构如图4所示。

4 打印机驱动设计

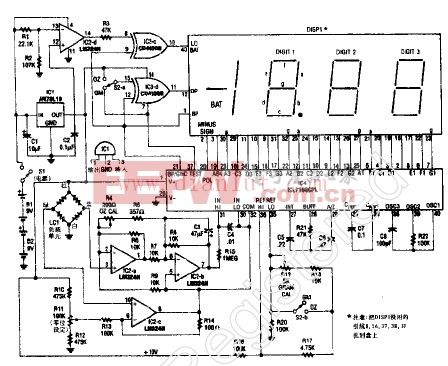

打印机是商用电子秤不可或缺的部件之一。热敏打印的原理是在控制逻辑的驱动下,通过控制打印头上排成方阵或条形式的微型发热器加热热敏纸使之产生一个与加热元素相同的图元,同时还控制进纸,以便印出整个图形(如销售商品条形码)。本文选用精工热敏打印机LTP1245,每一行384个加热点,最宽打印48mm宽带纸,打印加热电压范围4.2~8.5V,电源设计方便。为了减少打印电流,将每行分成六段,每段64点,分六次打印,其工作时序见图5。CLK是移位时钟信号,DAT是打印位数据,LATCH是数据锁存信号,DST是段控制信号。

打印数据在CLK时钟控制下从串行数据线DAT脚逐位输入打印机内,而后在LATCH锁存信号控制下保存在打印存储器中。数据全部锁存到数据存储器之后,在DST1-DST6信号的控制下分6次加热打印。当某路DST信号有效时,对应段被加热打印。384个数据位恰好对应384个加热点,当该位为0时不加热,打印纸上对应位置显白色,反之纸显黑色。打印加热时间由DST的持续时间控制,持续时间可以控制打印图形对比深度。根据图5中时序,结合上述设计思想,在CPLD中抽象出功能图如图6,Buffer1缓存步进电机驱动信号,驱动打印头四相精密步进电机,Buffer2缓冲打印头过热和缺纸传感信息。Buffer1的数据从P0口写入,Buffer2的数据被P0口读入。DECODER是译码器,译出6位打印机段加热控制信号,COUNTER实际上是串并转换器,将并行打印数据转换成串行数据以及移位时钟和锁存信号。

5 仿真验证

首先,使用硬件描述语言将每个独立的单元模块抽象出硬件实体,在EDA工具软件中调试通过并生成符号模型,然后再生成包含地址分配模块和接口部件的顶层文件,仿真出波形,完成整个设计。

图7为将CPU输入的并行数据转换成串行数据的打印机数据并-串转换仿真波形图,在图5的时序驱动下将串行数据输入到打印机。在MAXPLUS II中选定CPLD器件,对这一部分电路做timing analyzer分析,得到理论移位时钟的最高频率可以达到111MHz。这一结果的重要意义在于:假设一个并行数据需经过8个时钟后被移入打印机中,当CPU工作在40MHz时,若其发送一个并行数据到CPLD需要4个指令周期,每个指令周期需用12个机器周期,则CPU每发送一个并行数据的无间隔时间大约为(1/40)×4×2即1.2μs。可见,只要CPLD的并-串转换模块移位时间小于1.2μs即工作频率大于0.83MHz,即可实现单片机与打印机之间的零等待时间数据传输,这对于提高打印机打印速度非常有帮助。图5显示了将一个并行数据2移位的例子,最低位(LSB)最先从右边移出。

图8是PWM调制转换仿真验证波形图。PWM(Pulse Wide Moudulation)脉宽调制电路,实现将模拟信号转换成数字信号,是一种低成本高性能A/D采样方法。图中data_cnt计数器在data_en高电平信号作用下开始对clk脉冲计数,当data_en为低电平时停止计数,如果此时刚好rd也为低电平,则data_cnt被读出do数据线。很显然,这实际上是对data_en脉冲宽度计数。需要说明的一点是data_cnt为16位计数器,而CPU是8位,CPU在s控制信号的作用下分两次读出data_cnt数值。

本文论述了基于单片机和CPLD协同控制的商用电子秤设计方案,从应用角度着重研究了典型单片机应用系统中以CPLD作为逻辑控制部件的设计理念和实现方法,仿真验证了设计的正确性。其中面向存储器扩展、打印机驱动等问题的CPLD设计方法对CPU是透明的,其意义不仅在于可以提高系统的稳定性、减少CPU负荷、缩短调试周期和降低生产成本,而且可以泛化到DSP或其他类型CPU的应用系统中,因此具有推广价值。

评论