基于FPGA和DDS技术的软件无线电可控数字调制器的设计

引言

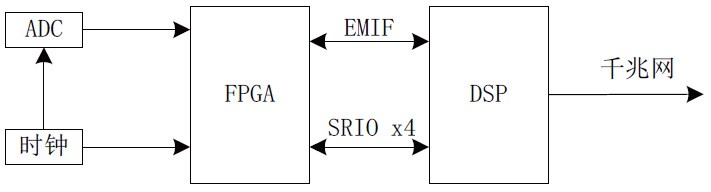

本文引用地址:http://www.eepw.com.cn/article/201706/349228.htm软件无线电是在无线通信领域提出的一种新的通信系统体系结构,其核心思想是以开放性、标准化、模块化的硬件为通用平台,通过在平台加载不同软件来实现对工作频段、调制解调、信道多址方式等无线功能的灵活配置。而调制解调技术是软件无线电的主要组成部分。直接数字合成技术(DDS)具有较高的频率分辨率,可实现快速的频率切换,能够保持相位的连续性,很容易实现幅度、频率和相位的数控调制。目前,软件无线电调制技术多采用具有调制功能的专用芯片或可编程器件和专用芯片相结合的方法实现,灵活性并不是很强。

基于此,本系统在分析数字调制技术和DDS原理的基础上,详述了一种基于FPGA的DSP技术和DDS技术的适合于软件无线电使用的可控数字调制器的设计过程,并在系统中进行了功能验证。此调制器以FPGA硬件平台为核心,可实现ASK,FSK,PSK,QAM等调制方式,灵活性强。

1 数字调制和DDS基本概述

在数字通信系统中,为了使数字信号能在带限信道中传输,就必须将编码后的信号进行数字调制。在此,主要分析和实现二进制单极性不归零码的键控调制。常见的二进制调制方式有ASK,FSK,PSK,QAM等。

直接数字合成(DDS)器具有数控频率合成的功能,它以数控振荡器的方式产生频率、相位和幅度可控的正弦波,电路主要由相位累加器、相位调制器、正弦ROM查找表、系统时钟、D/A、LPF等组成。本文中用DDS产生的正弦波作为载波,具有精确、灵活、便于集成等优点。DDS原理基本结构图如图1所示。

使用DDS结构易实现频率调制、相位调制和幅度调制,以DDS作为载波信号发生部分,具有频率稳定度高,频率转换速度快,输出带宽宽,频率分辨率高等特点。

2 基于FPGA的调制器的具体设计

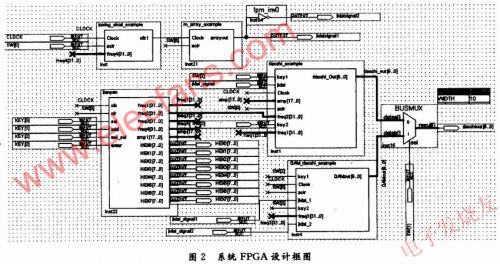

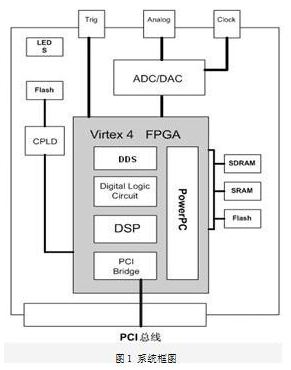

该设计借助QuartusⅡ7.2和Matlab/DSP Builder 7.2开发环境,在FPGA硬件平台上实现,最大限度的实现了集成化。图2是该设计的FPGA系统原理框图,数字功能模块全部集成在一片FPGA上,实现了SoPC的设计思想。

该设计由按键输入、二进制基带信号产生、数字调制和显示等模块组成,其功能是由按键输入设定值,同时在LED上进行显示,并根据设定值对二进制基带信号进行相应的数字调制,产生调制信号输出。现将各模块的具体设计和功能描述如下:

按键输入模块 输入采用按键和拨码开关实现,通过复用的方式用于选择调制方式,输入信号频率和幅度。在FPGA内部设计了一个按键接口模块,用于处理和存储输入的设定值,输出到LED显示,并输出相应的控制信号和调制模块所需的载波频率和幅度控制字等。

二进制基带信号产生模块 该设计中的基带信号由一个基于DDS的矩形脉冲发生器和伪随机序列M序列发生器产生。码元速率可通过按键模块输入频率字到矩形脉冲发生器控制输出脉冲频率,从而控制M序列输出频率来实现。当然,作为调制器,二进制数字基带信号是由外部输入的。本模块是为了验证系统功能和需要满足系统产生单纯的数字调制信号时而设计的,具体见系统原理图中juxing_signal和m_array_exa-mple模块。

数字调制模块 数字调制模块是整个系统的核心部分,包括ASK,FSK,PSK和QAM等数字调制方式。本模块以DDS为核心模型,采用Quart-usⅡ7.2和Matlab/DSP Builder7.2进行硬件的软件化设计,具体见系统原理图中tiaozhi_example,QAM_tiaozhi_example和BUSMAX模块。系统主要由时钟和复位输入端(CLOCK和SW[0])、调制方式选择输入端(SW[1],SW[2]和SW[3])、基带信号输入端(jidai_signal,jidai_sign-all,jidai_signal2)和频率幅度字输入端(freql[31..O],freq2[31..O],freq4[31..0]和amp[17..O])组成。频率和幅度字由按键输入实际频率和幅度值经过按键接口模块处理后,转化为32位频率字和18位幅度字,从而控制模块产生所需频率和幅度的载波信号。基带信号输入端接收被调制信号,被调制信号根据所选择的调制方式在模块内部进行相应调制后输出到模块输出端。

3 系统仿真和硬件实现与测试

在进行系统各模块设计的时候,为了防止在设计最后集成系统的时候出现功能错误,难于排查和修改,在设计过程中对各模块的功能正确性都进行了软件仿真。

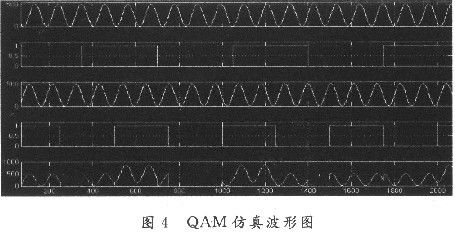

系统中的ASK,FSK,PSK和QAM波形仿真依次如图3和图4所示。

在确保各模块在独立状态下均能正确工作后,在QuartusⅡ7.2中进行系统集成,并对集成后的系统进行再次的整体仿真。接着,便可以进行功能测试。在功能测试中使用嵌入式逻辑分析仪SignalTapⅡ进行测试分析。在分析仪中进行相应的设置后,把它随设计文件一起下载入目标芯片中,用以捕捉芯片内部信号节点处的信号,并通过USB接口把数据传回计算机,并显示。以下是具体的测试过程,选择相应功能控制开关,用按键输入所需的载波频率值和幅度值,通过LED显示出来。相应的测试波形如图5所示。

2ASK功能测试(SW[1]=0,SW[2]=O,SW[3]=O):载波频率由freql输入设置,当基带码元为高电平1时,输出正弦信号;当为低电平0时,输出一个常数值,从而实现2ASK调制。

2FSK功能测试(SW[1]=O,SW[2]=1,SW[3]=1):载波信号频率由freql和freq2输入设置,当基带信号码元为高电平1时,输出频率为freql正弦波信号;当为低电平0时,输出频率为freq2正弦波信号,从而实现了2FSK调制。

2PSK功能测试(SW[1]=0,SW[2]=O,SW[3]=1):载波信号频率由freql输入设置,但同时控制了正弦查找表和余弦查找表,当基带信号码元为高电平1时,控制正弦表输出正弦波信号;当为低电平0时,输出余弦波信号,从而实现了2PSK调制。

QAM功能测试(SW[1]=1,SW[2]=1,SW[3]=0):载波信号频率由freq3输入设置,同时控制了正弦查找表和余弦查找表,两查找表信号相互正交,两路基带信号码元分别乘上正余弦查找表输出信号,然后将输出信号进行叠加,从而实现了QAM调制。

4 结语

该设计完全在一片FPGA芯片上完成,减少了硬件的搭构,具有很高的集成度。采用DDS技术为核心,使载波信号获得了较高的性能。借助强大的开发工具和FPGA的可重复编程及动态重构特性,使设计更具灵活性和通用性。系统设计了按键输入和处理模块,能根据需要变更载波频率,并通过LED直观显示出来。重点对调制模型进行了设计,并进行了系统级仿真和最后的硬件功能测试,达到了设计的具体要求。

评论