基于FPGA的JPEG解码器设计与实现

随着多媒体技术的蓬勃发展,视频编解码技术得到了长足的进步,人们先后制定了多个数字图像视频编解码标准。其中JPEG仍然是目前最流行的静止图像压缩格式,在手持设备和网络中有广泛的应用。

本论文工作是无线投影机控制器设计中的一部分,见图1。该控制器以开放源代码处理器LEON3为核心,具有以太网、VGA、PCI等接口,PCI接口用来连接无线网卡,VGA接口用来连接投影机,这样构成一个无线投影系统。PC机通过有线网络或无线网络向控制器传输JPEG压缩图像数据,经过解码器解码后显示在投影仪上,从而实现多台电脑共享一台投影机,并且避免了连线的麻烦,具有一定的市场前景。考虑到系统的灵活性,本控制器选用Altera FPGA作为实现平台,设计可以无缝地转移到Altera Hardcopy技术,从而实现低成本。

本设计利用硬件描述语言(VHDL)设计了JPEG Baseline的解码系统。

1 JPEG解码器原理

JPEG解码器主要由四部分组成:图像头信息的读取、熵解码、反量化、IDCT(反离散余弦变换),其数据流图见图2。

从图中可以看出,解码器首先从JPEG图像数据中读取Header信息,得到与解码相关的如哈夫曼表、量化表以及图像大小等信息,并且将这些信息存储在RAM或者寄存器中,供后面的步骤调用。

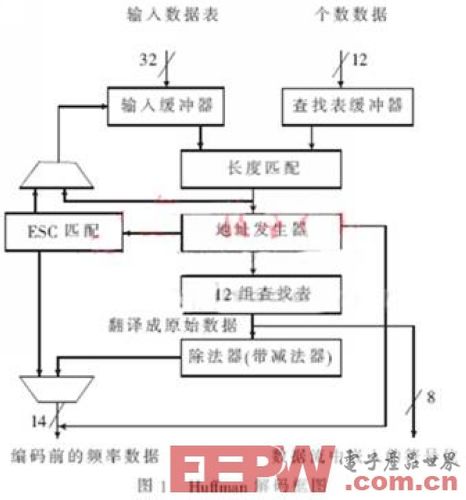

在图像头信息读取完成后,解码器进一步读取压缩编码的数据并对其进行熵解码。压缩编码的数据采用哈夫曼(Huffman)编码。哈夫曼编码是一种常用的压缩编码方法,是Huffman于1952年为压缩文本文件建立的。它的基本原理是:将频繁使用的数据用较短的代码代替,而较少使用的数据用较长的代码代替,每个数据的代码各不相同。这些代码都是二进制码,且码的长度可变,因此哈夫曼编码是可变长编码的一种。在JPEG中采用游程编码与范式huffman编码进行数据的压缩存储,并且直流系数(DC)与交流系数(AC)分开编码,提高了压缩效率。因而在熵解码过程中需要分别对直流系数和交流系数分别解码。当前直流系数为上一个直流系数加上当前熵解码数据(即残差)。

当解码完一个MCU(Minimal Coded Unit)后,接下来就是进行反量化的操作,即将解码出来的数据乘以一个量化系数。

最后是IDCT(反离散余弦变换)操作,即DCT(离散余弦变换)的反变换。离散余弦变换(DCT)是N.Ahmed等人在1974年提出的正交变换方法,它常被认为是对语音和图像信号进行变换的最佳方法。通过DCT变换,将数据从一个域变换到另外一个域,其大多数高频分量的系数变为0。人眼对低频分量比较敏感,对高频分量则不太敏感;因而量化的结果是去掉了不太重要的高频分量,降低了码率。在JPEG解码过程中需要通过IDCT还原图像原始数据。IDCT部分是计算量最大的单元,对此单元设计的好坏将直接影响到解码速度。

2 JPEG解码器设计与实现

针对JPEG解码流程特点,本JPEG解码器硬件总体设计如图3所示。JPEG CONTROLLER负责调度各个模块的执行;Src_ram存储着JPEG原始图像数据;Addr_gen模块产生下一个需要读取字节的地址;Read_markers模块读取JPEG图像的图像头信息,并且将头信息保存在Register files中,相应的量化表信息及huffman表将存储在Dqt rams和Dht rams中;Huff_derived_tbl是由huffman表生成的用于熵解码的表格;Decode MCU 模块从Src_ram读取JPEG图像数据并解码,解码出来的数据将逆zig-zag顺序存储在Block ram中;IDCT模块读取Block ram中的哈夫曼解码数据进行反量化和IDCT变换,之后将数据输出到Ram。下面将对各个模块的设计作详细的介绍。

2.1 Addr_gen模块设计

此模块用于产生读取Src_ram的地址并生成下一个要读取字节的地址。其硬件实现如图4虚线右边部分所示。在非跳转情况下,当RD信号有效时,Addr_gen计数器每次递增1个单位。

跳转情况下,即skip有效时,其计数器工作如图4虚线左边部分所示,当读入地址为Addr_n的数据后需要跳转k个单位的字节(Skip_num=k),因为在读取地址为Addr_n的数据Data_n后地址计数已经增加了一个单位,因而在第三个时钟周期能跳转到地址为Addr_n+1+k的数据,而这第三个时钟周期读出来的数据Data_n+1将会被忽略。从第四个时钟起此模块将恢复正常的读取数据功能。

2.2 Read_markers模块设计

Read_markers读取JPEG文件头信息并且解释,由以下子模块组成,见图5虚线左边部分。

(1)First_marker:判断文件是否为JPEG文件,即判断开始的2B是否为FF D8;

(2)Next_marker:查找下一个标志;

(3)Get_sos:读取sos(start of scan);

(4)Skip_var:跳过一些信息时被调用,给Addr_gen模块传送跳过信息标志;

(5)Get_sof:读取sof(start of frame);

(6)Get_dht:读取huffman表信息,存储在Dht rams(见图1);

(7)Get_dqt:读取量化表信息,并存储在Dqt rams(见图1);

(8)Get_dri:读取重起间隔,以MCU(Minimum Coded Unit)为单位。

硬件实现利用FSM(有限状态机)来进行控制。其模块调度示意图见图5虚线右边部分。

2.3 Decode_MCU模块设计

Decode_MCU是jpeg解码器设计中一个非常重要的单元,也是正式解码的开始。本设计中此模块的设计见图6虚线框中设计,主要由四个子模块组成:Fill_buffer、Decode_blockIZZ、Process_restart和Controller。

(1)Fill_buffer:当32BITS_REG中的比特数不够时控制器将启动此模块读取Src_ram中的数据并且加载到32bits_reg中,并且去掉码流中的填充数据。

(2)Decode_blockIZZ:huffman解码,并且将解码数据逆zig_zag顺序输出。

(3)Process_restart:当JPEG图像中有restart interval(Get_dri)标志,在解码完由Get_dri规定的n个MCU后,控制器首先调用此模块来进行同步(在网络传输中非常重要)。

(4)Controller:控制协调各模块的执行。

核心模块Decode_block硬件实现如图6,虚线右边是EXTEND[1]部分,采用查找表实现。Get_buffer即图6中的32BITS_REG, Bits_left记录32BITS_REG中剩余的比特数。Huff_D模块每启动一次解码一个熵编码数据。由于DC编码采用DPCM编码,解码直流(DC)时需要增加一个时钟周期来加上上一个DC的值,从而得出如图6所示的output,解码交流系数(AC)时则在EXTEND后直接输出。Sel_s_input为”00”时,选通huffman解码数据;为”01”时,选通EXTEND后的数据;为”10”时,选通加上了last_dc_val的数据。

2.4 IDCT模块设计

IDCT(Inverse Discrete Consine Transform)是JPEG解码器中最耗资源和计算量最大的单元。本设计为减少内存读取,提高解码速度,将反量化也放在IDCT模块中实现。

离散余弦变换的公式和离散余弦逆变换的公式如下:

经分析公式(1)可以做如下等效变换:

即通过两次一维的IDCT变换即可实现二维的IDCT。考虑到数据的读取,本设计IDCT模块的设计如图7虚线框中所示。

实现过程:首先读取Block ram的一列,相应的反量化数据从Dqt ram中读取,经过IQ(反量化单元,即乘法器)后的8个数据存储在regs中,之后控制器启动一维IDCT变换,并将反变换后的数据存储在REG FILES的一列中。当一个Block ram中的8列数据全部反量化和IDCT变换后,控制器将切换成对REG FILES中一行的数据进行一维IDCT变换,变换后的数据存储在REG FILES中的一行中,之后再进行下一行变换,直到8行数据全部IDCT 变换完。基于参考文献[2]的一维IDCT实现具有资源比较小和实现简单的特点,通过对IDCT反变换矩阵系数分析,一维IDCT奇偶数据变换具有不同的结构化特点,在此可以进行单独的设计,最后将两部分的结果数据进行碟形加减操作,得到一维IDCT的运算结果(见图7)。这样变换完的数据即可进行输出,送到显示单元进行色彩变换和其它后续处理后显示。

2.5 测试与结果

本设计采用的硬件开发平台为ALTERA DE2,FPGA为EP2C35F672C6,在quartusii 5.0中进行综合,所耗资源和最大时钟频率见表1。2005年ACTEL[3]公司推出的JPEG-D IP的速度针对不同的平台其速度变化从31M~69M,同年4I2I[4]公司推出的JPEG-D的最大速率为40M,从速度可以看出本设计达到了实时解码的要求。

将VHDL与C语言实现的JPEG解码器对图像解码产生的结果进行对比,从而可以判断解码正确与错误。通过结果对比,本设计结果完全正确。

本设计严格按照VLSI自顶向下设计的一般流程,首先进行C语言级建模[5],从而得到测试矢量和JPEG硬件解码器的总体架构;之后完成了各个顶层模块和子模块的接口定义;最后进行各个模块的VHDL实现。从结果可知达到了实时解码要求,并且节约了资源。

评论