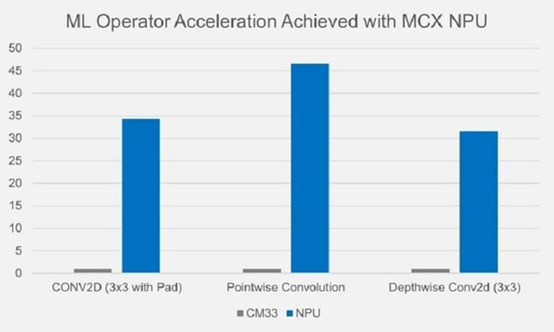

锂离子电池管理芯片的研究及其低功耗设计 — 锂离子电池管理芯片的电路实现 (二)

4.2.2振荡器

本文引用地址:http://www.eepw.com.cn/article/201706/348223.htm1电路结构

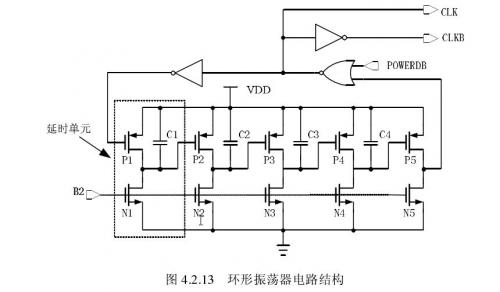

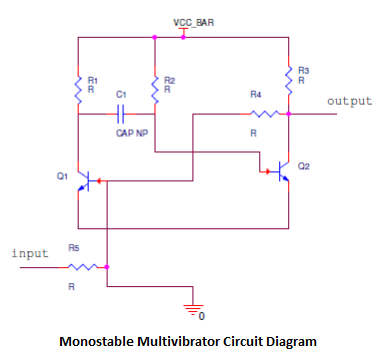

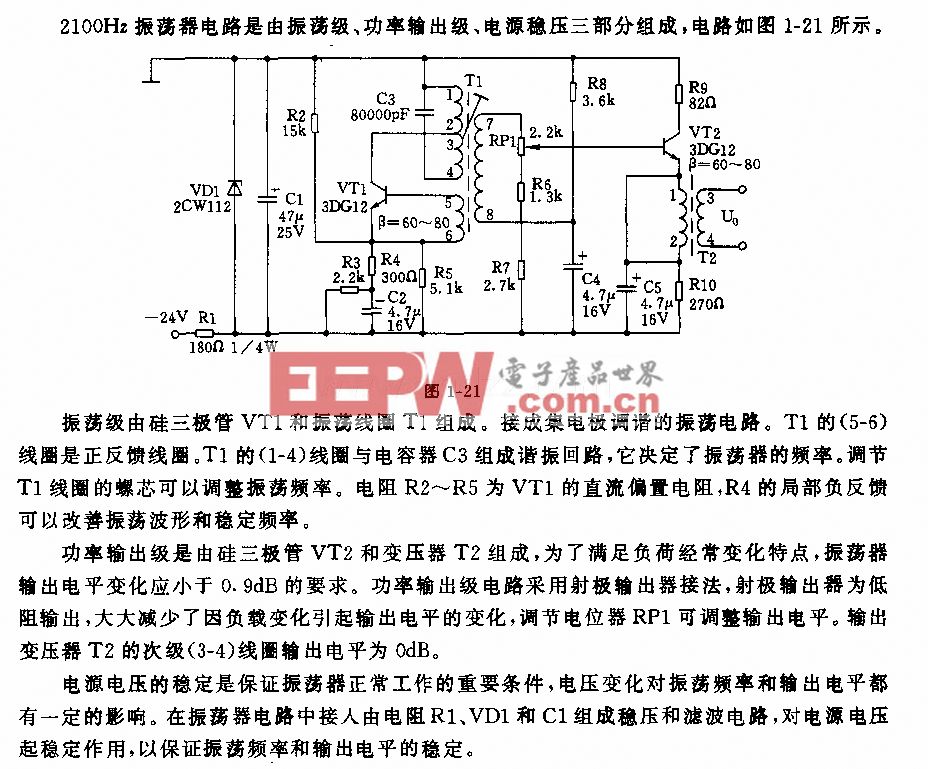

延时电路设计中,一个重要的部分便是振荡器。电池管理芯片中的振荡器,必须能在较宽的工作电压范围(1.5V~8V)内、在各种工艺和使用条件下输出频率相对稳定的时钟信号,而且电流消耗要足够低。除负载短路外,电池产生过充电、过放电和过流等意外情况发生后,允许存在的时间均在ms级;又考虑到延时时间参数的设置和频率对功耗以及亚阈值电 路的影响,振荡器的频率设为2kHz.振荡器结构中,RC振荡器是常见的一种,其输出频率受阈值电压影响较小,但是受电源电压影响较大;Relax振荡器是另一种常见结构,其结构简单,输出频率受电源电压变化影响较小,但是在电容放电时,存在从电源到地的通路,因此并不适合在低功耗场合使用。而环形振荡器结构简单,通过改进易于实现低电流消耗,所以本文设计了一个环形结构的振荡器,电路如图4.2.13所示。

图 4.2.13中,偏置电路通过B2端给NMOS提供栅级电压,即给振荡器提供了电流源I CTRL;POWERDB信号由逻辑控制电路输出,正常情况下为低电平,当电池电压降低到一设定值时,系统进入Power Down状态,POWERDB将变为高电平,此时振荡器输出为零。

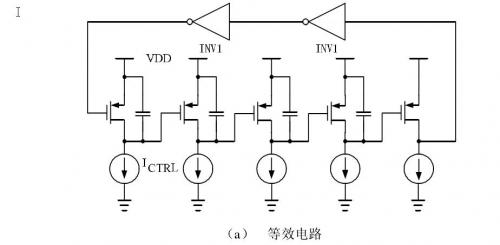

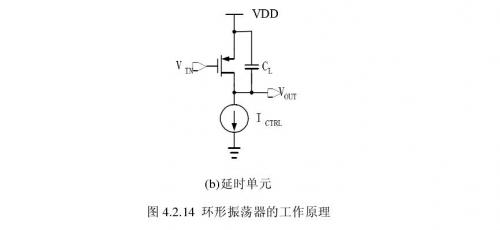

正常工作时,振荡器的等效电路如图4.2.14所示。在正常情况下,振荡器由5个电流源负载反相器和2个推挽反相器组成,反相器数目为奇数,所以振荡器振荡,输出一对频率相同、相位相反的矩形波CLK和CLKB.从图4.2.13可知,第5个电流源负载反相器中,负载电容是或非门的输入栅极电容,该电容很 小,因此该反相器的上升延时和下降延时很短。同样,推挽反相器的上升延时和下降延时通常在ns级,对于低频振荡器也可以忽略。所以,振荡周期主要由前四个电流源负载反相器的上升延时和下降延时来决定。可将前四个电流源反相器视为延时单元,如图4.2.14(b)所示。在估算振荡器的振荡周期时,只需要考虑 延时单元。

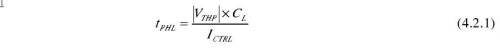

显然,延时单元的上升延时和下降延时,与其充放电速率及负载电容CL相关。由图4.2.14(b)可知,当输入VIN变为高电平时,PMOS管关断,电容CL开始恒流放电,VOUT电平将下降至使下一级PMOS管导通。将这期间所经历的时间计为下降延时tPHL,有

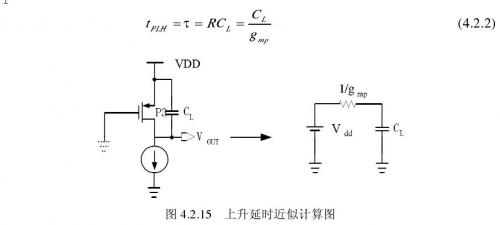

式中,VTHP为PMOS阈值电压。反之,电容CL充电时,VOUT由低电平将上升至下级PMOS管关断,所经历的时间定义为上升延时tPLH。由图4.2.15的上升延时近似计算图可以近似求出tPLH为

式中,gmp为PMOS管的跨导。一般地,CL取2pF左右,提高电源电压和增大PMOS管的宽长比可以增大gmp,从而减小上升延时。和下降延时相比,上升延时较小,估算时可以忽略不计。

因此,振荡频率fOSC可以表示为

式中,N为电流源负载反相器数目,此处有N=4.由式(4.2.3)可知,在不考虑工艺容差和负载电容值偏移情况下,振荡频率误差主要由电流源所提供的电流稳定性所决定,所以振荡器希望电流源是一个理想的恒流源,并且有很高的电源电压抑制比。

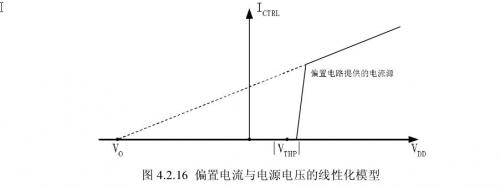

2振荡频率误差因素而在实际应用中,并不存在理想的恒流源,偏置电路提供的输出电流ICTRL和电源电压的关系,可由图4.2.16所示的线性化模型来表征。

图4.2.16中,当电源电压在1.5V到8V之间变化时,ICTRL近似线性上升。(4.2.3)式则可变为

式(4.2.4)中,k是斜率,单位为欧姆。式(4.2.4)表征了振荡器的振荡频率与电源电压V DD、|VTHP|及CL之间的函数关系。下面讨论各因素变化对输出频率稳定性的影响:

当VDD固定不变时,|VYHP|变化时,对(4.2.4)两边求导有

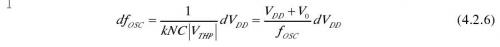

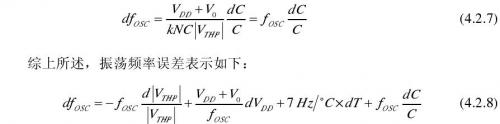

当|VYHP|固定不变时,VDD变化时,对(4.2.4)两边求导有

当温度变化时,其他参数不变,温度升高时,振荡频率上升,反之下降。温度变化时,振荡频率变化主要是PMOS管的阈值电压随温度变化。由于阈值电压与温度之间的关系很复杂,所以通过模拟来确定温度与振荡频率之间的关系。

模拟结果表明,温度变化,其他参数不变时,振荡频率随温度近似线性上升,估算时取(Δfosc/T)≈7Hz/℃。

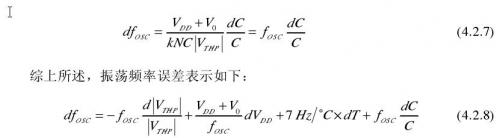

当电容C变化,其他参数不变时,对(4.2.4)式两边求导有:

由(4.2.8)式可知,振荡频率误差也与振荡频率值有关。降低振荡频率,将在一定程度上减小振荡频率误差。对于给定的振荡频率,要想减小振荡频率误差,从根本上应使偏置电路的输出电路更接近恒流。

3波形及噪声考虑

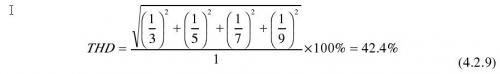

同一频率的周期矩形波和方波信号频谱中,谐波的幅度以1/n规律收敛。方波的偶次谐波落在频谱包络线的零值点上,所以它的频谱只包含基波和奇次谐波分量,所以和同一振荡频率的矩形波相比,方波具有最小的谐波失真(THD),即有

设计时调整C1的电容使得输出波形CLK和CLKB接近方波。

时钟抖动和相位噪声描述的是同一现象,都指的是振荡器输出的不确定性。

两者不同之处在于时钟抖动描述输出时域的不确定性,而相位噪声则描述输出频域的不确定性。

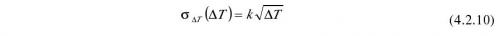

开环系统中,绝对时钟抖动与测量间隔的平方根成正比,如下式所示

式 中k为比例系数,T为测量间隔。在锂离子电池管理芯片中,由于振荡器作用于计数器的时间间隔固定(等于3Tosc、5Tosc、7Tosc、 12Tosc),而且系统延时容许的误差远远大于测量间隔期间的绝对时钟抖动,故振荡器对相位噪声没有严格的要求,尽管如此,设计中还是采取了一些措施来 减小相位噪声。

研究表明,低频电源噪声和高频衬底耦合噪声对环形振荡器的相位噪声影响最大,所以要尽量减小电源噪声和衬底耦合噪声。而图 4.2.13所示的电路中,延时单元的负载电容不接地而接电源电压即是为此目的。从NMOS管的源极看进去,NMOS和C L组成低通滤波器,能够有效滤除数字电路的开、关通过衬底引入振荡器的高频噪声。

同时,根据线性时变模型(LTV)的研究可知,不对称的上升和下降沿将增加1/f3角频率,从而增大相位噪声和时钟抖动,使得THD变大。1/f3角频率随着振荡器的级数增大而减小,因此设计时振荡器采用七级反相器,既可以减小1/f3角频率、减小THD,同时有利于产品的系列化。

评论