基于ADF4106的低相噪本振设计

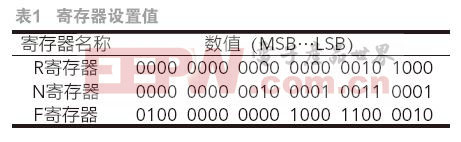

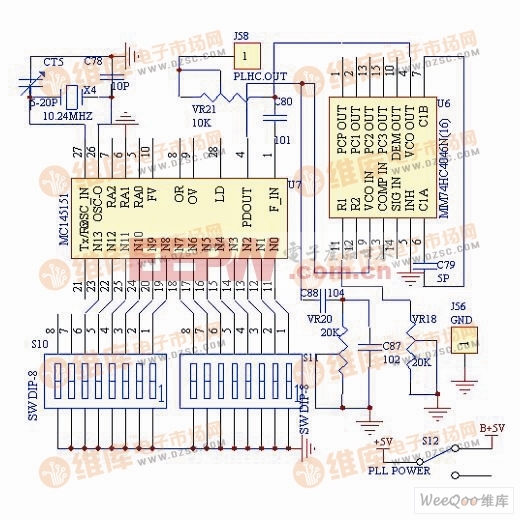

可以得出锁相环输出频率。其中,![]() 为压控振荡器的输出频率,P为双模式前置分频器的预设模式,B为二进制的13位计数器预设分频比,A为二进制的6位计数器预设分频比,为外部提供的参考频率,R为参考频率的分频比。根据方案要求,ADF4106的各个参数设置为:P=16,B=33,A=12,R=10。三个控制寄存器初始化设置为R寄存器000028h,N寄存器002131h,F寄存器4008c2h,如表1所示。送数时序如图3所示。

为压控振荡器的输出频率,P为双模式前置分频器的预设模式,B为二进制的13位计数器预设分频比,A为二进制的6位计数器预设分频比,为外部提供的参考频率,R为参考频率的分频比。根据方案要求,ADF4106的各个参数设置为:P=16,B=33,A=12,R=10。三个控制寄存器初始化设置为R寄存器000028h,N寄存器002131h,F寄存器4008c2h,如表1所示。送数时序如图3所示。

2.2 环路滤波器设计

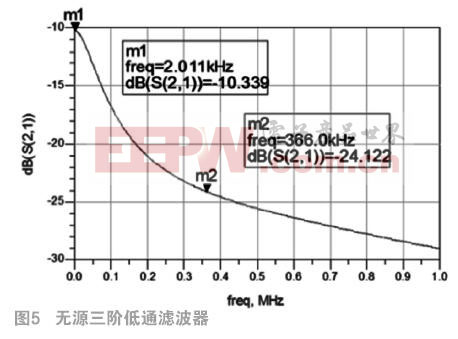

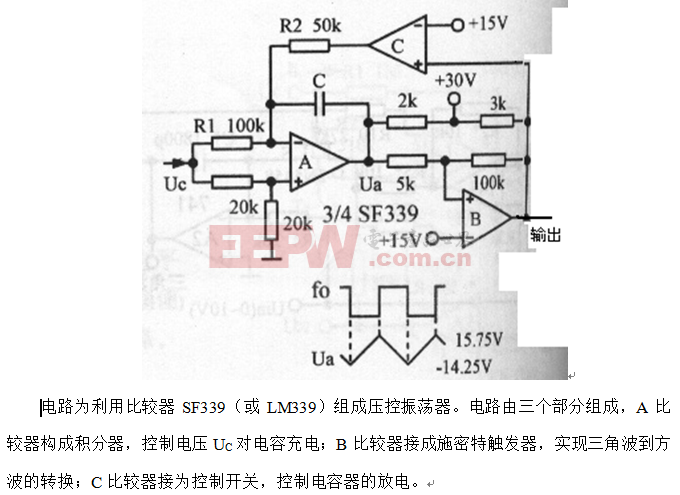

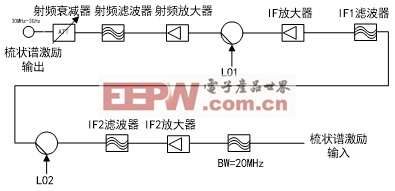

锁相环路滤波器电路是锁相环电路中重要的一个部分,它的性能直接影响环路的稳定性、锁相时间和锁相输出的相位噪声、杂散指标等[5]。本方案设计中的环路滤波器是用来将ADF4106充电泵输出的鉴相电流转换成驱动压控振荡器的控制电压,同时抑制高频分量。在实际的电路实现中,由于鉴相频率在锁相环输出上会产生寄生杂散,而二阶环路一般不能滤除,所以采用三阶低通滤波器,提高了对杂散频率的抑制程度。因为相对于无源环路滤波器,有源环路滤波器电路复杂程度增加,同时噪声也相对较高,所以通常设计中都是优先选用无源环路滤波器。本方案利用ADI公司提供的PLL仿真软件ADIsimPLL ver3.0设计三阶无源环路滤波器,如图4所示。电容C1的作用是将ADF4106电荷泵输出的脉冲转化成直流电压,电容C2和电阻R1的目的是增加环路的稳定性,电阻R2和电容C3能够抑制干扰纹波,同时滤除由鉴相频率带来的杂散分量。利用仿真获得的三阶无源滤波器图形如图5所示,仿真结果是理想值,经过多次实际调试获得最佳参数。

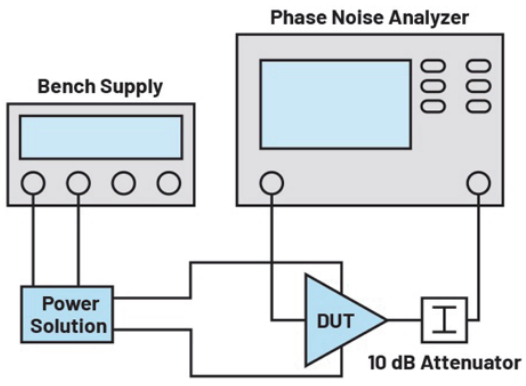

2.3 功率调理电路设计

因为测试仪器要求第二点频本振的输出功率范围是10~12dBm。而测得压控振荡器经过功分器输出信号的功率是0.5dBm,所以需要设计功率调理电路对第二点频本振的输出功率进行调整。功率调理电路包括放大器和数控衰减器。本设计选用ADI公司的放大器HMC313和数控衰减器HMC425LP3,通过送数控制HMC425LP3的衰减量,测得第二点频本振的输出功率是11dBm,送给HMC425LP3的数据是3Bh。

3 测试结果

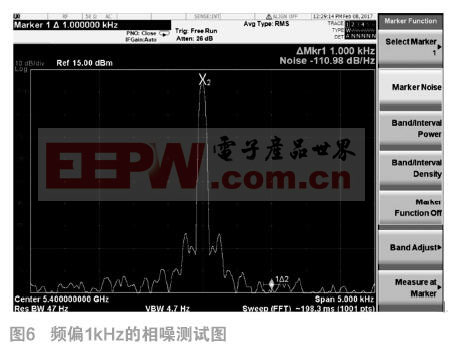

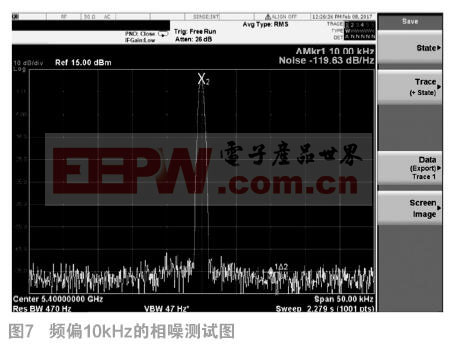

根据本方案设计的低相噪点频本振经调试后满足相噪指标和功率指标要求。图6、图7分别是用频谱分析仪测得的1kHz、10kHz频偏的相位噪声。1kHz频偏的相位噪声是-110.98dBc/Hz,10kHz频偏的相位噪声是-119.63dBc/Hz。

4 结论

本文设计了一种基于锁相环芯片ADF4106的低相噪本振源,通过对锁相环路滤波器的优化设计和实际调试,测得相位噪声满足设计指标要求,通过对输出功率调理电路的设计、调试,使得本振输出功率为11dBm,满足设计指标10~12dBm的要求。本文设计的本振源已成功用于一款通信测试仪器中。

参考文献:

[1]陶长亚.基于HMC833LP6GE的宽带本振源设计[J].电子产品世界,2016,331(23):31-33.

[2]赖一成,宋亚梅.S波段低相噪振荡器的设计[J].信息技术,2013.2:140-145.

[3]李昂,于萌,朱康生.宽带低相噪频率综合器设计与实现[J].电子科技,2015.28(7):54-59.

[4]梁刘永,张龙.X波段低相噪跳频源的设计与实现[J].电子设计工程,2012,20(4):135-138.

[5]白居宪.低噪声频率合成[M].西安交通大学出版社,1994,10.

本文来源于《电子产品世界》2017年第6期第30页,欢迎您写论文时引用,并注明出处。

评论