利用Cortex M7紧密耦合内存运行快速算法

对于那些需要低功耗、成本效益和中等性能的嵌入式系统而言,ARM Cortex M系列无疑是首选的处理器系列。 Cortex M系列中最早得到应用的是其光谱中的小部分产品: Cortex M0用于实现最低的成本,Cortex M0+用于实现最高 的能效,Cortex M3用于实现功耗与性能之间的最佳平衡, Cortex M4用于实现那些需要数字信号处理(DSP)功能的应 用。

该系列中最高性能的Cortex M7的首批应用现已开始涌 现。该处理器在保持适度能耗和成本的情况下,能以更快速 度运行更加复杂的算法。Cortex M7 采用65-nm嵌入式闪存工 艺,运行频率为300MHz时CoreMark分数可达到1500,而且 其DSP性能是Cortex M4的两倍。一个双精度浮点单元和一个 双发指令流水线进一步确立了Cortex M7的高速地位。凭借这些特性,当低功耗、低成本应用需要严密的音 视频算法来实现丰富的影音功能时,Cortex M7成为了它们 当仁不让的选择。 Cor tex M7在无人机图像处理、 语音控 制、物体识别、复杂的汽车传感器融合以及高端物联网传感 领域得到了广泛应用。

1 可快速、确定地执行代码的紧密耦合内存

为了实现实时响应和无缝的音视频性能,FIR、FFT、 Biquad等算法经常需要尽可能快速、确定地运行。为了满足 系统的性能和时延目标,这些算法应以全时钟频率运行,不 受缓存未命中、中断、上下文交换以及其它有损时间确定性 的执行意外阻碍。

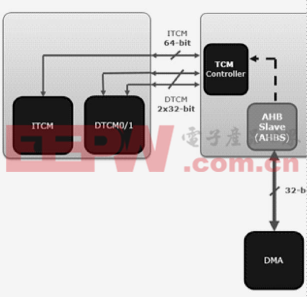

这意味着您不能在标准内存之外运行这些代码,也不 能依赖标准内存来存储正在处理的数据。闪存等典型内存的 速度太慢,跟不上Cortex M7内核的脚步,而且它们需要缓 存,所以,当发生缓存未命中时会导致较长的时延。因此, Cor tex M7架构提供了一种方法, 使用“ 紧密耦合内存”(TCM)来绕开标准的执行机制。A R M 的 内 核 提 供 T C M 接 口 , 用 于 实 现 以 处 理 器 全速 运 行 的 单 周 期 随 机 TC M 存 取 。 一 个 6 4 位 指 令 内 存 端 口(ITCM)支持双发处理器架构,两个数据端口(DTCM) 能够实现两个并行的32位数据存取。但该架构没有指定应 提供内存的类型以及大小。这些决定留由那些在微控制器(MCU)中实现Cortex M7内核的设计人员作出,目的是鼓 励创新和差异化设计。

因此,我们可以将嵌入式闪存连接至TCM接口。但闪 存不能以处理器全速运行,因此需要缓存,从而给TCM旨 在提供的确定性带来了威胁。DRAM中的代码映射在理论上 可行,但成本过高。速度达到能够实现无缓存、直接存取的 唯一内存类型就是SRAM。

SRAM具备众多优势:可以将一个SRAM模组直接连接 到TCM接口;SRAM技术便于实现片上嵌入;SRAM支持处 理器全速随机存取。SRAM的唯一缺点是位成本较高,高于 闪存和DR AM。因此,重要的是要保持有限的TCM大小, 即使是65nm或40nm的工艺也能以适当的成本实现充足的 SRAM容量。

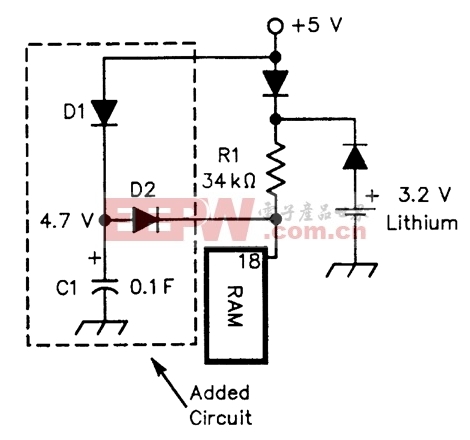

TC M 可 从 多 个 来 源 加 载 , 而 这 些 来 源 在 架 构 中 也 未 明确指出。因此,各种MCU可能在内存加载方式上存在差 异,必定包含的是一个直接内存存取(DMA)引擎,而至 于是一个单一的DMA,还是来自视频或USB等不同数据流的 多 个 加 载 数 据 之

一 , 这 个 由 M CU

设计人员决定。

在 T C M 之 外 执 行 的 代 码 由 系 统 编 程 人 员 确 定 。 在 准 备 一 个 软 件 构 建 时 , 编 程 人 员 需 要 确 定 应 用 在 T C M 上的 代 码 段 和 数

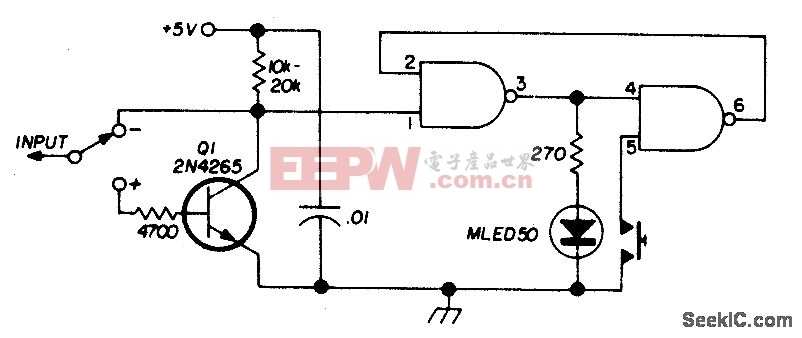

图1 TCM接口提供一个单一的64位指令端口和两个32位数据端口

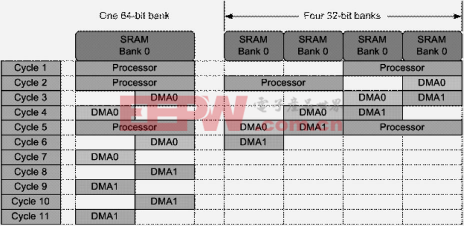

图2 将SRAM应用到内存条时,多个DMA突发传送会同时引发微量时延

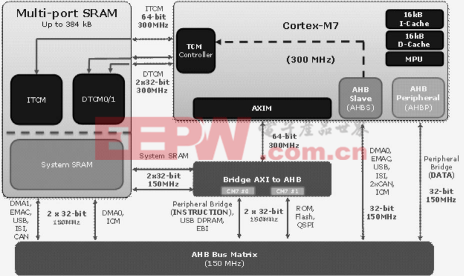

图3 Atmel SAM S70/E70系列可使用TCM或系统SRAM的SRAM提 高灵活性和利用率

据块。通常是将Pragmas嵌入到软件中,或者应用链接器设 置,以便让该构建能够合理地放置代码和内存。

2 用于更高速SRAM存取的多个端口

虽然TCM可提供一个用于快速、紧密运行重要程序的 直接机制,但我们经常需要将一定容量的系统SRAM配置为 通用高速内存,供处理器和外设通过DMA使用。虽然这种 内存在逻辑上与TCM分离,但一个SRAM模组也能共享TCM 和通用功能,而且还能让设计人员为每种应用情况对TCM 和系统SRAM之间的分离作出调整。

通用系统SRAM中实现的外设数据缓冲区通常由DMA传 送且通过系统外设加载。但是,从众多来源加载的能力会引 发多个DMA试图同时存取内存,从而导致不必要的时延和 冲突的可能性。

在一个典型的例子中,有三个不同的实体对SR AM的 DMA存取进行相互竞争:处理器(64位存取,而在本例中 要求是128位存取)和两个分离的外设DMA请求(DMA0和 DMA1,均为32位存取)。让我们假设处理器的优先级高于 DMA,而DMA0的优先级高于DMA1。

图2 显示了这个例子。左侧显示了一个64位宽式单条内 存的性能,右侧显示了由4个32位内存条组成的同一个内存 中处理相同事务。

使 用 单 条 内 存 时 , 处 理 器 可 以 在 两 个 周 期 内 完 成 存 取, 然后, DM A0突发在下一个周期启动。 DM A1会被锁 定,直至DMA0完成。任何优先级更高的处理器请求都会中 断DMA加载,从而进一步增加时延。如图2所示,周期5中 的一个取指令给两个DMA操作增加了一个周期时延。

为了提高操作效率,可以使用配有交错地址的多个内 存条组成一个内存,每个内存条可以被单独存取。在这种方 法中,DMA0会在处理器存取完第一个内存条时启动,而在 同时,处理器会存取高优先级的内存条。DMA1不再需要等待整个DMA0传送结束,它可以在DMA0存取完第一个内存 条之后的一个周期中启动。

由于具备更高的优先级,处理器看不出这两种方案在 时延上的差别。但DMA0的时延从2个周期缩短为1个周期, DMA1的时延从7个周期缩短为2个。DMA操作期间的一个取 指令甚至可能会与DMA操作同时发生,从而导致无附加时 延。更低的时延不仅提高了性能,同时也意味着您可以缩小 外设FIFO。

有了这些可行且有用的内存方案,MCU设计人员将能 设想如何让闪存、系统SRAM和TCM配合工作。它们是相互 独立吗?占用类似的容量吗?芯片上还是芯片外?不同的考 量将催生出差异化的Cortex M7。

3 一个具体的Cortex M7 TCM实例

Cortex M7 MCU的一个实例在Atmel的SAM S70、SAM E70和SAM V70/1系列中实现。它拥有一个由4个内存条组 成的SR AM,可被用作通用SR AM(Atmel将其称为“系统 SRAM”)和TCM。在被配置为TCM的部分中,指令能够以

300 MHz的内核全速运行确定性的单周期存取,无取指令或 缓存时延。与此类似, TCM中的数据也可以实现无缓存时 延存取。

指令TCM(ITCM)和数据TCM(DTCM)大小必须类 似,每个可以是32K、64K或128K字节。尺寸是不能轻易更 改的构建时设置。

整 个 S R A M 模 组 最 大 可 为 3 8 4 K 字 节 , 这 意 味 着 系 统 SR AM和TCM可以同时使用。配置为TCM的内存容量将占 用系统SRAM的容量。例如,如果ITCM被配置为128 KB, D T C M 也 被 配 置 为 1 2 8 K B , 那 么 系 统SR A M的容量将降至128 KB。 系统SR A M能够以最高150 MHz的速度运行,即一半的处理器速度,而且它由四个内存条组成,可降低DMA时 延。既可固定也可循环设置的DMA存取优先级与系统SRAM 相同,因为它们针对的是内部总线矩阵。

一个寄存器位可激活或取消激活TCM,因此,存取目 标将取决于TCM激活。设备总是在ITCM取消激活时被引 导,以便让代码能够从引导内存加载。引导完成后,需要时 可以激活TCM。

ITCM地址空间与引导内存叠加。如果取消激活TCM, 指令存取将前往引导内存。如果激活TCM,TCM地址空间 中的存取将在TCM中进行,TCM空间以外的存取将在闪存 中进行。可以使用MPU保护各个空间,以确保不会发生对错误

内存的无意存取。4 Cortex M7是下一波ARM内核

Cortex M7正在兴起,运行更加高级的算法,同时依然 保持适度的功耗和成本。紧密耦合内存是Cortex M7的一大 特性,能够以处理器全速确定地执行紧密的代码。

如 何 在M CU 上 是 实 现 这 种 性 能 将 取 决 于 设 计 人 员 将 Cortex M7集成到MCU中时的系统选择。我们可以将SRAM 配置为TCM来实现最高的速度。这个SR AM可以与一个更 为通用的系统SR AM共享, 而且通过使用多个内存条组成 SRAM,可以将时延降至最低。

这些架构特性虽然简单,但却能够显著提升性能,实

现个人、工业和汽车设备所需的嵌入式功能。

评论