先进封装工艺WLCSP与SiP的蝴蝶效应

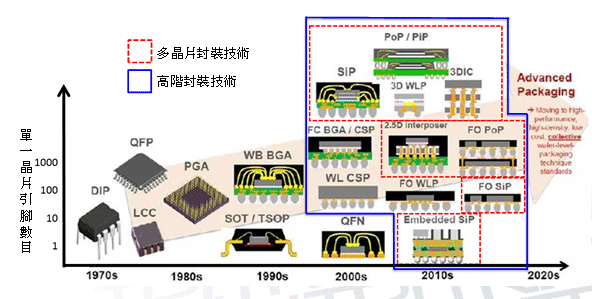

关于先进封装工艺的话题从未间断,随着移动电子产品趋向轻巧、多功能、低功耗发展,高阶封装技术也开始朝着两大板块演进,一个是以晶圆级芯片封装WLCSP(Fan-In WLP、Fan-out WLP等)为首,功能指向在更小的封装面积下容纳更多的引脚数;另一板块是系统级芯片封装(SiP),功能指向封装整合多种功能芯片于一体,压缩模块体积,提升芯片系统整体功能性和灵活性。

本文引用地址:http://www.eepw.com.cn/article/201610/310984.htm图1:主要封装形式演进

Source:拓璞产业研究所整理,2016.9

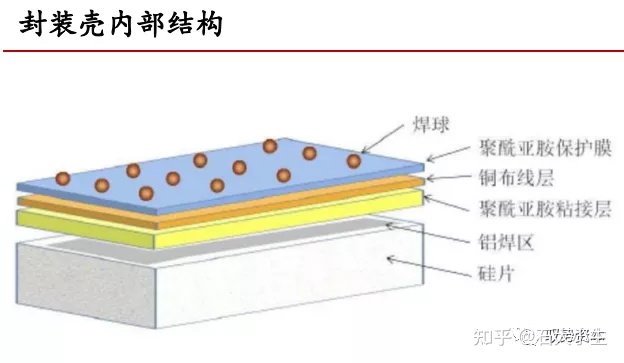

WLCSP:晶圆级芯片封装(Wafer Level Chip Scale Package)也叫WLP。与传统封装工艺相反,WLP是先封装完后再切割,因此切完后芯片的尺寸几乎等于原来晶粒的大小,相比传统封装工艺,单颗芯片封装尺寸得到了有效控制。

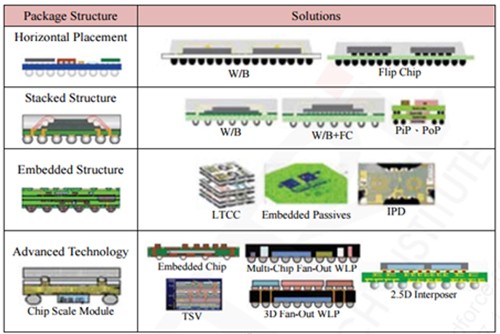

如何在更小的尺寸芯片上容纳更多的引脚数目?WLP技术利用重分布层(RDL)可以直接将芯片与PCB做连接,这样就省去了传统封装DA(Die attach)段的工艺,不仅省去了DA工艺的成本,还降低了整颗封装颗粒的尺寸与厚度,同时也绕过DA工艺对良率造成的诸多影响。

起初,Fan-In WLP单位面积的引脚数相对于传统封装(如FC BGA)有所提升,但植球作业也仅限于芯片尺寸范围内,当芯片面积缩小的同时,芯片可容纳的引脚数反而减少,在这个问题的节点上,Fan-out WLP诞生,实现在芯片范围外充分利用RDL做连接,以此获取更多的引脚数。

图2:从传统封装至倒装封装及晶圆级封装结构变化示意图

Source:拓璞产业研究所整理,2016.9

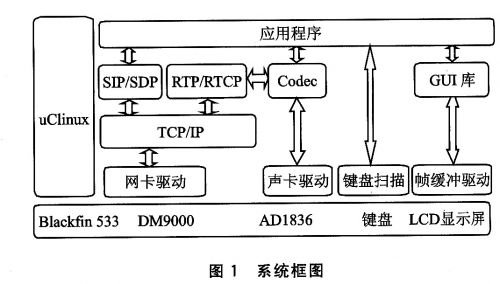

SiP:将不同功能的裸芯片通过整合封装的方式,形成一个集多种功能于一体的芯片组,有效地突破了SoC(从设计端着手,将不同功能的解决方案集成与一颗裸芯片中)在整合芯片途径中的限制,极大地降低了设计端和制造端成本,也使得今后芯片整合拥有了客制化的灵活性。

另外由SiP延伸的3D堆叠式封装技术,通过在垂直方向上增加可放置晶圆的层数来进一步提高SiP的整合能力,可以说作为异质整合的标杆,SiP在超越摩尔定律方面扮演着头号角色。

图3:SiP 的基本分类

Source:拓璞产业研究所整理,2016.9

评论