基于FPGA的实时视频图像采集与显示系统的设计与实现

摘要:主要针对目前视频图像处理发展的现状,结合FPGA技术,设计了一个基于FPGA的实时视频图像采集与显示系统。系统采用FPGA作为主控芯片,搭栽专用的编码解码芯片进行图像的采集与显示,主要包括解码芯片的初始化、编码芯片的初始化、FPGA图像采集、PLL设置等几个功能模块。采用FPGA的标准设计流程及一些常用技巧来对整个系统进行编程。重点在于利用FPFA开发平台对普通相机输出的图像进行采集与显示,最终能在连接的RCA端口显示屏显示。

关键词:FPGA;视频图像采集;编码芯片;解码芯片

0 引言

随着时代的发展,人们在图像处理领域取得了相当多的成果,研究出了很多算法,例如中值滤波、高通滤波等。在图像的传输过程中,各种噪声源的干扰和影响常常会使图像的质量变差。由于用一般的软件实现的图像预处理算法处理的数据量大,实现起来会比较慢,如果说对于一些实时性要求比较高的系统,那么处理速度往往是要考虑的关键要素,因为一旦实时性达不到,就不能第一时间记录下信息。另外,实时图像处理技术的日新月异和图像处理系统的发展有着千丝万缕的联系。在实时图像处理系统中,关键的技术是对实时图像的采集和处理,图像采集的速度、质量直接影响到这个系统的性能。

1 系统硬件设计

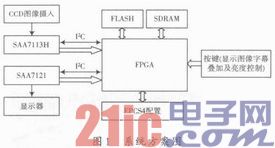

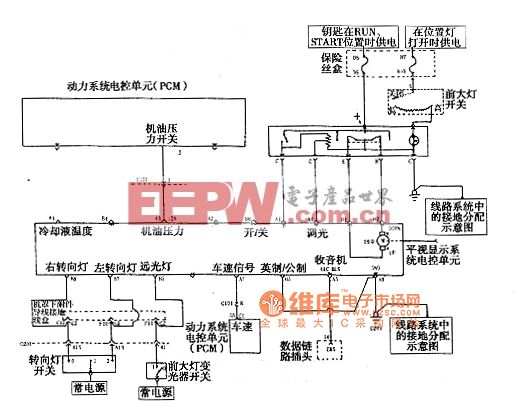

本系统基于FPGA的实时图像与显示系统,由前端视频采集单元、图像存储单元、图像显示单元三部分组成。主要功能为对摄像头送来的视频数据进行采集,并采用专用视频解码芯片将模拟视频转化成数字视频;将采集进来的数据存储到内嵌的SDRAM中;采用专用视频编码芯片将数字视频信号转换为模拟信号送显示器输出。系统的方案图如图1所示。

系统上电后,FPGA管理单元通过I2C总线对SAA7113H解码芯片进行初始化;CCD摄像头输出的PAL制式模拟视频输入SAA7113H解码模块。FP GA将解码后的图像通过输入缓冲FIFO存放到外部SRAM;再用SDRAM进行奇偶场的合并,满一帧后图像进入FPGA进行内部图像处理,经输出缓冲进入SAA7121编码模块转换为模拟视频输出。通过按键的选择可控制使其输出图像亮度增强及字符叠加。本节将围绕系统中的视频图像解码芯片及编码芯片作具体分析。

1. 1 解码芯片外围电路

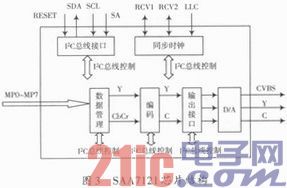

SAA7113H主要由模拟转换电路、亮度信号电路、色度信号电路、同步电路、输出信号格式、总线控制及时钟生成等组成。AI11、AI12、AI21、AI22为四路模拟输入通道,AOUT为模拟测试输出通道,VP00~VP07为解码输出通道,这些通道的选择及格式配置都通过I2C总线来完成的。另外,SDA为I2C总线的数据输入/输出端,SCL为串行时钟输入端,LLC为行锁定系统时钟频率输出信号,频率为27 MHz,XTALI、XIAL是外部晶振连接端,TDO/TDI为边界扫描测试数据的输出/输入端,TCK、TMS为边界扫描的时钟和测试模式输入端。SAA7113H的芯片结构图如图2所示。

1.2 编码芯片外围电路

SAA7121视频编码芯片,可以将数字的YUV数字编码为PAL或者NTSC制式的CVBS输出或者S端子输出的模拟视频信号,单一的3.3 V供电,可通过I2C接口对芯片内部电路进行控制。该芯片内有三个片内10位视频D/A转换器分别对应Y,C和CVBS,两倍过采样。通过I2C总线协议对SAA7121的各个控制寄存器进行配置就可使其满足系统要求,芯片的最大特点也是在于仅需一个24. 576 MHz的晶振就可以满足所有视频标准的应用。

SAA7121芯片主要由I2C总线控制单元、数据管理单元、编码单元、同步时钟单元和D/A转换器组成。主要通过I2C总线对芯片的内部寄存器进行设置,也就是完成对芯片的工作属性的设置。输出数据的格式有两种:复合视频输入信号(CVBS)或分离视频信号,输出的制式可以为NTSC制式或PAL制式,支持隔行扫描和连续扫描方式,并具有Y、C和CVBS三个信号的数膜转换器。

SAA7121主要由数据管理模块,总线接口模块,编码模块,D/A模块组成。MP0~MP7是MPEG端口,输入CCIR.656的Cb—Y—Cr的编码数据;RCV1为栅控制端,输入或输出各种类型的信号;LLC为线性锁定时钟,为芯片提供27 MHz的主频;CVBS为模拟CVBS信号输出,C为模拟色度信号输出,Y为模拟亮度输出。SAA7121通过设置内部寄存器,对其进行初始化。SAA7121的芯片结构图如图3所示。

2 系统软件实现

通过在FPGA开发平台上,使用QuartusⅡ9.0对系统进行硬件语言编程。本系统主要由SAA7113H解码芯片初始化模块、SAA7121编码芯片初始化模块、FPGA视频图像采集与显示模块组成。

2.1 SAA7113H初始化模块

SAA7113H的初始化模块主要分为I2C控制核模块,I2C命令模块,ROM模块。I2C控制核心模块完成数据的并/串转换以及将命令转换位为I2C总线的SCL/SDA信号线的启动、停止、写、应答等具体操作的时序关系;I2C命令模块则是通过状态机(FSM)的方式进行I2C接口间状态的转换以及从ROM模块中将配置好的数据输出给I2C控制核模块,ROM模块存储的是配置好的SAA7113H的数据。当启动I2C开始配置时,从ROM中读取配置的内容送出即可。

2.2 SAA7121初始化模块

SAA7121编码芯片的初始化和SAA7113H有些类似,都是通过I2C总线来控制芯片内部寄存器实现初始化的目的。SAA7113H解码芯片中的I2C控制模块分为核心模块和命令模块,而SAA7121编码芯片则只包含一个I2C模块。

在SAA7121的寄存器配置模块中,首先,上电复位,确保SDA,SCL为高电平,随后将SDA从高电平拉到低电平,发出I2C总线起始信号,开始I2C总线操作。接着向I2C总线写芯片的从地址,SAA7121芯片地址也与输入引脚SA电平及读写操作有关。SAA7121芯片的输入引脚SA是接地的,因此芯片地址为SA低电平时的地址。在写入芯片地址后,再读应答,并确认有应答时,再写寄存器的子地址。同样在确认有应答时,再写入寄存器数据通过循环将要配置寄存器的所有数据依次写入到I2C总线上。最后,在全部数据写完后,发出I2C总线中止信号。

2.3 FPGA图像采集与显示模块

系统中最核心的地方就是图像的采集与显示,包括FPGA采集与存储模块,FPGA显示模块两块内容。视频图像采集模块的主要作用是接收来自CCD摄像头的模拟信号,经视频输入处理芯片SAA7113H,输出ITU656 4:2:2格式的数字图像。完成视频信号从模拟信号到数字信号的转换,最终提供后端可以处理的数字视频数据,存储到SDRAM中。

3 功能实现与测试

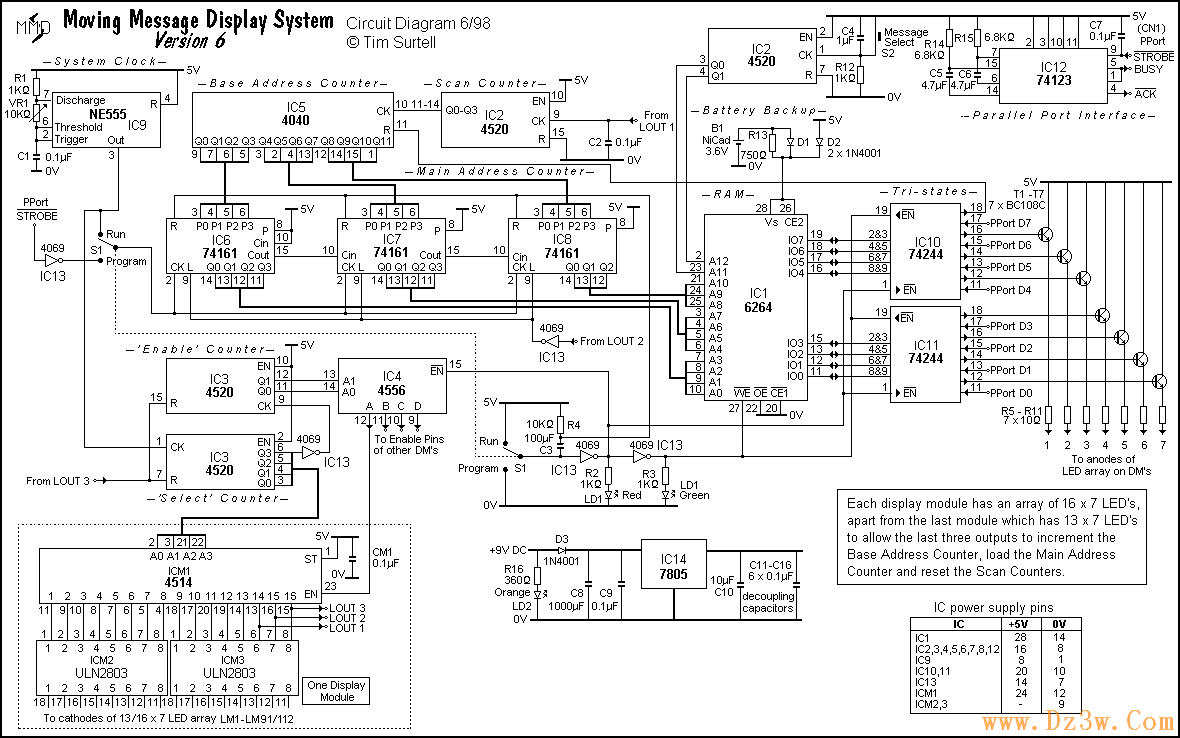

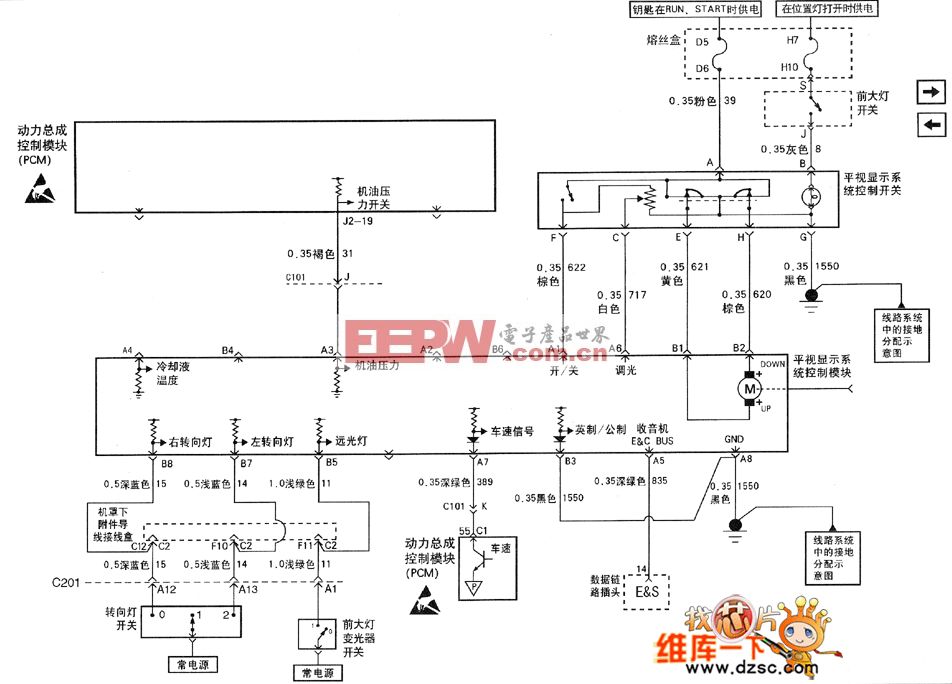

系统连接图如图4所示。通过对系统进行编程,完成系统的软件设计,按照FPGA的设计流程完整的测试了系统的可行性,包括:系统的输入输出环路测试(能否实时的显示图像),系统的按键调控亮度测试(解码芯片功能)。测试图如图5所示。

4 结语

结合国内实时图像采集处理系统的现状,本设计在硬件上采用FPGA作为核心运算器来实现图像的采集、存储和显示;在硬件实现上使用FPGA硬件描述语言Verilog对系统各个功能模块进行设计。采用FPGA可编程逻辑设计技术实现视频图像采集与显示系统不仅拥有极大的灵活性,可编程性,而且也加快了图像采集与显示的速度。由于本文设计的系统中未涉及到复杂的算法,而是用专用的编码芯片代替了,所以在本文中,图像的算法未能加入到系统中。下一步的工作就是学习将高端FPGA芯片运用到图像处理技术当中去,结合网络技术,研究更新的视频图像采集与显示技术。

评论