基于FPGA的短波AM解调器的设计

摘要:调幅是中短波广播中一种主要的调制方式。本文针对现有的模拟短波AM解调器的不足,提出了一种基于FPGA的全数字解调器。其最大的优点是将系统中的模拟电路压缩到最小。短波信号在前端经过模数转换器采样后直接送给FPGA处理,有效的避免了过多的模拟电路对系统指标的影响。

本文引用地址:http://www.eepw.com.cn/article/201610/308478.htm短波通信是历史最为久远的无线通信,被广泛地应用于政府,外交,气象等领域。由于短波通信设备简单,机动灵活,成本低廉,传输距离远并且信道不易被摧毁,在通信领域占有极其重要的地位。在有些短波监测应用中需要在几十公里外的地方监测AM电台,这就需要将短波信号解调后再通过光纤传输到监测台。传统的短波接收机采用超外差技术,首先通过模拟器件将射频信号变换到为中频信号,再对信号进行放大、滤波、解调等处理,这使得系统抗干扰能力差。现在也有一些数字短波接收机,在中频对短波信号数字化,再利用DSP实现短波解调。由于依然使用到了太多的模拟器件,使得系统性能提升有限。本文根据软件无线电的思想,提出一种全数字的短波解调器。使用高速模数转换器直接射频采样,并将高速数据流送给FPGA完成下变频、滤波、解调。此系统将模拟器件压缩到最小,使得系统的抗干扰能力得到极大的提高,这也将系统的解调灵敏度提升到了一个新的高度。

1 AM解调原理

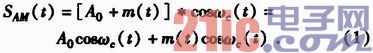

AM信号的时域表示式分别为:

式中,A0为外加的直流分量;m(t)可以是确知信号也可以是随机信号,但通常认为其平均值为0.即m(t)=0。

AM信号的解调方法有两种:相干解调和包络检波解调。

1.1 相干解调

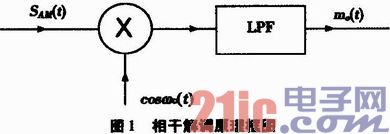

已调信号的频谱搬回到原点位置,即可得到原始的调制信号频谱,从而恢复出原始信号。解调中的频谱搬移可以使用相乘运算来实现。相干解调的原理框图如图1所示。

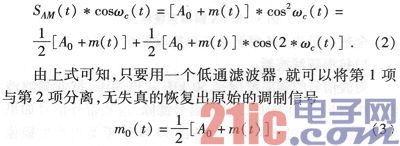

将已调信号乘上一个与调制器同频同相的载波,得

相干解调的关键是必须产生一个与调制器同频同相位的载波。如果同频同相位的条件得不到满足,则会破坏原始信号的恢复,因此在实际应用中很少使用。

1. 2 包络检测法

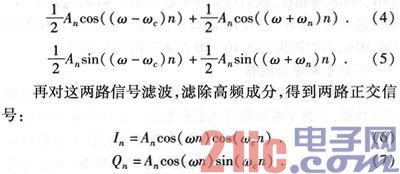

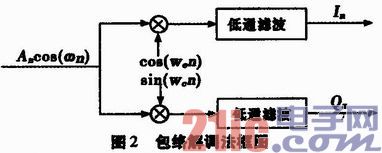

将信号与一正交载波相乘,如图2,得到两路信号:

包络检测法对载波信号要求不高,是现在较为常用的短波AM解调方法。

2 基于FPGA的AM解调算法实现

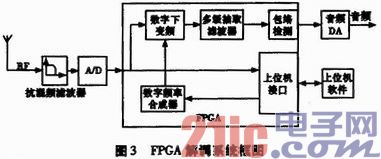

模拟解调用模拟器件完成射频信号的下变频、滤波、解调。现有的数字中频解调也是利用模拟器件将射频信号下变频到中频信号,再通过模数转换器转换成数字信号,最后送给DSP完成解调。在此方案中也同样需要模拟器件完成信号变频、滤波,这使得此系统的性能相对于纯模拟解调方法提高有限。本文提出的利用FPGA实现短波解调,首先使用高速模数转换器直接在射频阶段完成数字化,再由FPGA完成滤波、抽取、变频,将高速宽带宽数据转换为低速、带宽为2KHz的窄带宽数据,最后根据包络检测法解调出音频信号。具体实现过程框图如图3。

全数字短波AM解调系统包括以下6个部分:

1)抗混频滤波器

短波信号的频率范围是50 kHz~30 MHz,抗混频滤波器的作用是将30 MHz以外的信号滤除,这些带外信号如果没有被滤除,经过AD采样后将在30 MHz带宽内产生镜像频谱,在最后解调出的AM信号中出现杂音。

2)模数转换器

模数转换器完成射频信号的数字化工作。由于是对射频信号直接数字化,根据奈奎斯特采样定理,射频信号的带宽是30 MHz,则采样率需达到60 MHz。为了得到更好的SNR,SFDR等指标,我们将采样率定为100 MHz,选用的AD采样芯片为linear公司的LTC2217,此芯片的最高采样率为105 MHz,可以提供高达105 dB的无杂散动态范围。

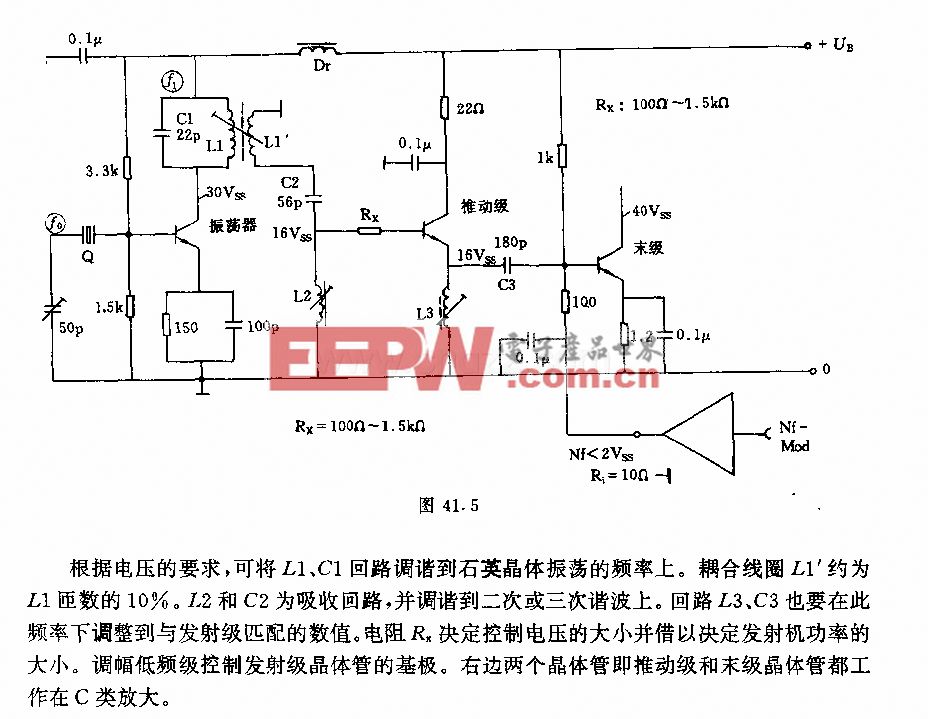

3)数字频率合成器

数字频率合成器的作用是根据给定的频率产生对应的正弦数据,为数字混频器提供混频数据。常用的实现方法有查找表法和Cordic算法。基于查找表的数字频率合成器实现过程简单,但需要占用大量的存储器资源,而且精度与存储器空间大小有直接关系,存储器空间越大,精度越高。Cordic算法比较复杂,但基于流水线结构的Cordic算法只需移位和加减法操作就可以完成,FPGA资源占用少。其精度与流水线级数相关,实际情况中可以根据需要选取适当的级数。具体原理在AM包络检测中详细介绍。

4)数字混频器

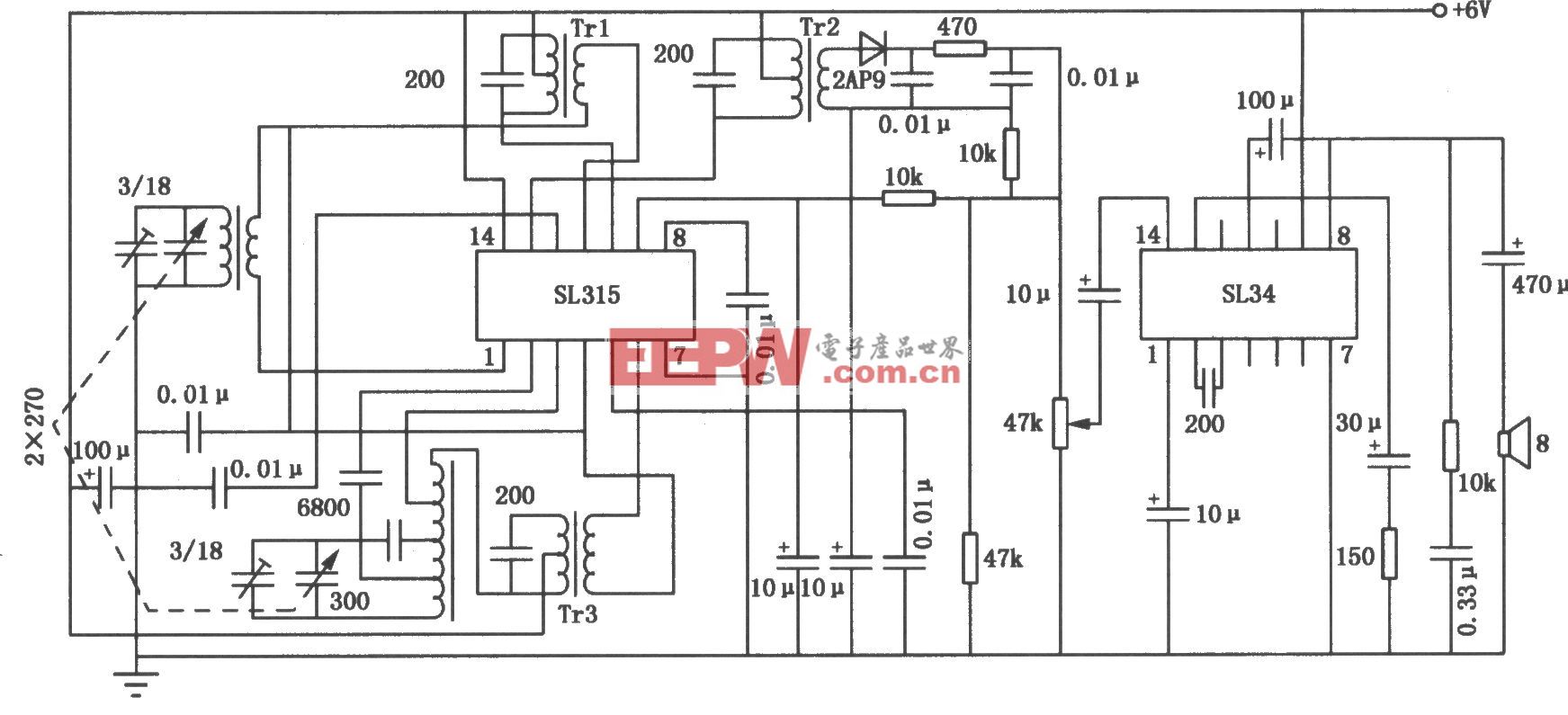

与数字中频解调系统类似,全数字解调系统需要将待解调信号从射频变频到中频。具体的实现过程如图4所示。

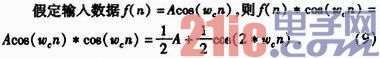

高频成分cos(2*wcn)由低通滤波器滤除,在本系统中wc定义为待解调的信号频率。通过数字混频器将待解调信号搬移到零频点附近,为下一级数字抽取做准备。FPGA算法实现如下:首先通过上位机软件设置wc,FPGA内部的数字频率合成器生成相应频率的正弦数据,利用FPGA的乘法器完成相乘操作。将乘法器输出的数据送给数字滤波模块,就可以将完成频谱搬移。

5)多级抽取滤波器

多级滤波器是本系统中最重要的部分,其直接关系到整个解调系统的最终性能。短波信号在经过AD采样后转换为速率为100 MHz,带宽为50 kHz~30 MHz的高速数字信号。而在整个短波波段中有上千个频道,每个频道的带宽只有2~10 kHz,因此需要将单个频道数据从30MHz带宽的数据中提取出来。如果直接在100 MHz频率范围内设计一个10 kHz带宽的带通滤波器,这样的滤波器通带要求非常窄,过渡带要求非常陡,此滤波器系数将达到几百甚至一千,这对滤波器的实现带来很大的困难,容易使系统的特性非常的不稳定。因此在实际的设计中,一般都采用多级结构进行分级滤波和抽取,以求降低对抗混叠滤波器的要求。将抽取因子D分解为J个整数的乘积,即:

,此系统可用J级整数因子级联的形式来实现,如图5所示。

图中第i级输出序列的采样频率Fi=Fi-1/Di,hi(n)是第i级抗混频滤波器,其阻带截止频率为:Fsi=Fi/2=Fi-1/2Di,以此设计的每一级抗混频滤波器可以保证各级抽取后没有混频现象。

6)包络检测器

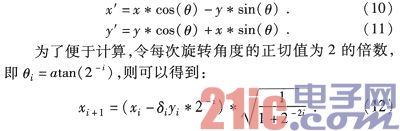

包络检测是将滤波器提取出的窄带AM信号通过两个相互正交的信号相乘,滤除高频分量后,对这两路信号取均方根。本文通过cordic算法能够快速计算出其包络。原理如下:

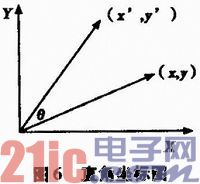

假设直角坐标系内有一个初始向量v(x,y),旋转θ角度后得到另一个向量v’(x’,y’),如图6所示。

由图6可得:

将此计算值转换为16 Bit的双字节发送给音频DA就可以得到调制在短波信号上的原始音频信号。

3 设计流程及结果分析

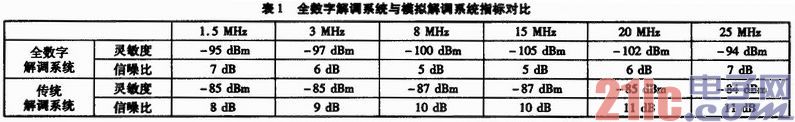

系统设计包括算法仿真,FPGA软件设计实现。算法仿真通过MATLAB实现,主要包括FIR设计,Cordic算法设计,对滤波后的数据进行频谱分析以验证算法的正确性。FPGA设计采用Synopsys公司推荐的设计流程。由于本系统中的模拟器件较少,避免了信号每经过一级模拟器件所产生的劣化,因此全数字解调系统的灵敏度有很大的提高,对调制信号信噪比的要求有很大的降低。通过将此系统与其他模拟解调系统的灵敏度以及对调制信号所要求的最低信噪比所做的对比(表1)得出,本系统在信号很微弱的情况下依然能够解调出满足人听觉的音频信号。

评论