面向消费类媒体产品设计的模拟/RF设计自动化技术

处理器、显示技术、压缩算法和无线数据通信等众多领域的进步正在造就新一代具有丰富功能的消费类电子产品。为了在这个诱人的市场取得成功,制造商们需要新的设计方法,使他们能够以更快的速度向市场推出更多功能、更低成本和更低功耗的产品。

本文引用地址:http://www.eepw.com.cn/article/201610/307845.htm下一代消费类媒体产品的最大设计挑战是如何设计低功耗的模拟和RF接口,并把这些接口与嵌入式系统的其余部分集成在一起。工艺技术的惊人进步使得系统级芯片(SoC)设计可以实现以前无法达到的集成度,但这也增大了模拟/RF设计挑战的难度。前几代工艺使设计人员能够把数字功能集成在单芯片上,而由系统板上的分立芯片提供其余功能。实际上,余下功能主要包括RF、模拟或混合信号电路。SoC革命则允许把所有这些功能都集成到单芯片上。

这种集成可以带来众多好处,包括减少系统组装成本、降低功耗和增强可靠性。这些因素对于提高在消费类媒体产品市场上的竞争力是至关重要的。据IBS公司的统计分析显示,在2000年,混合信号半导体的毛利润比纯数字产品高10-12%,而且混合信号产品的年降价幅度不到数字产品的1/3。因此,混合信号产品不仅能带来更高的利润,而且这种利润是不断增长的。如果哪家公司能够成功地利用新一代工艺技术来提高集成度、降低系统成本和功耗,那么它在市场上将获得比竞争对手更大的利润,并取得更大的成功。

SoC设计者面临的关键挑战

不幸的是,这种令人向往的集成还存在某些问题。造成这些问题的根源在于模拟与数字电路之间的根本差异。与模拟电路不同,数字电路的可收缩性非常好。随着工艺特征尺寸的缩小,数字晶体管变得更快、更冷、更便宜。因为数字晶体管只须寄存1和0,所以它们不会受工艺或温度差异的影响,事实上,两个设计类似的数字晶体管虽然可能包含实际缺陷,但在功能上仍是等效的。

然而,在模拟电路中,即使两个模拟晶体管的物理实现有略微的不同或者它们的工作环境稍有变化,都将导致两个晶体管出现不同的行为,从而产生问题。随着特征尺寸的缩小,“不匹配”问题将变得越来越严重,因为小的瑕疵会由于器件面积的缩小而被放大。此外,不断缩短的栅极长度将使电流密度、功率密度和电压噪声增大,从而减少了噪声裕量。在130纳米工艺下,长期被设计者忽略的漏电功率将变成一个限制因素。以下由东京大学 Takayasu Sakurai教授提供的数据说明了SoC设计者必须克服的一些挑战:

* 栅极长度 ×0.5* 功率密度 ×1.6

* RC延时/瞬态延迟×3.2

* 电流密度 ×1.6

* 电压噪声 ×3.2

(注:乘法因子表示参数的变化倍数)

此外,妨碍把模拟和数字功能集成到单芯片上的其它问题还有许多,包括衬底耦合噪声、欧姆压降,以及最重要的一点,即如何实现功耗预算目标。

如果这些问题加在一起,其复杂性将令设计者无法对付。东芝公司向IEEE电子设计过程(EDP)工作组提交的一份报告说明了这种情况。在该报告中,东芝讨论了用于模/数转换器的一种比较器电路的设计,它由0.25微米工艺移植到0.13微米工艺需要四周时间。这种再设计过程要求设计师在确定21种器件参数(7个堆栈式晶体管的宽度、长度和m因子)的同时,努力实现最小的功耗。

模拟、混合信号设计自动化

模拟/混合信号设计自动化技术可以从两个方面使这些问题得到一定缓解。首先,随着常规设计任务的复杂性增加,自动化技术越来越能够在更短的时间内找到等同于或者比人工设计方式更好的解决方案。我们曾在20世纪90年代从数字逻辑综合方面观察到这种现象,即当设计算法和设计复杂性达到某种程度时,自动化技术将成为优先考虑的选择。今天,我们在模拟电路领域再次看到这种现象,由于设计算法已经十分成熟,设计又达到足够的复杂度,以致于自动化解决方案成为设计者的首选。

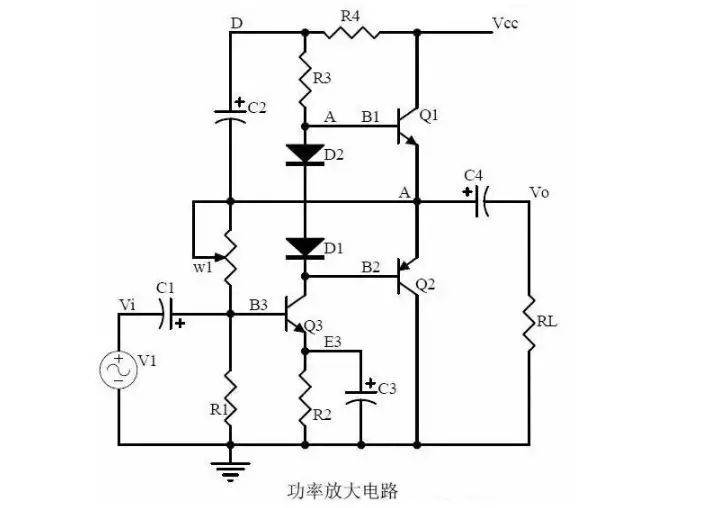

其次,通过自动完成那些当今占用设计者大量宝贵时间的常规任务,设计者可以支配更多时间来进行能取得更大价值回报的设计活动。图1以一个典型的压控振荡器(VCO)为例说明了这点。如果不采用任何自动化技术,设计者的大部分时间不是用在做设计上,而是浪费在缩小尺寸、布局和实现设计收敛等常规任务上。最新一代的模拟/混合信号设计自动化工具能够为设计者提供功能强大的自动化流程,使设计者可以用更多时间来做增值设计。这对于在消费类产品领域取得成功是至关重要的,在这些领域,要满足更低的功耗预算需要选择恰当的架构。

有希望的结果

为了在消费类媒体产品市场取得成功并从混合信号SoC中获得更大利润,制造商需要解决模拟/混合信号(A/M-S)设计的瓶颈。主要EDA供应商已经认识到克服A/M-S设计挑战的重要性。Cadence公司IC实现部总经理Lavi Lev表示,模拟设计将是实现SoC远景蓝图的关键。此外,几家小型的新兴公司正致力于解决A/M-S设计挑战。

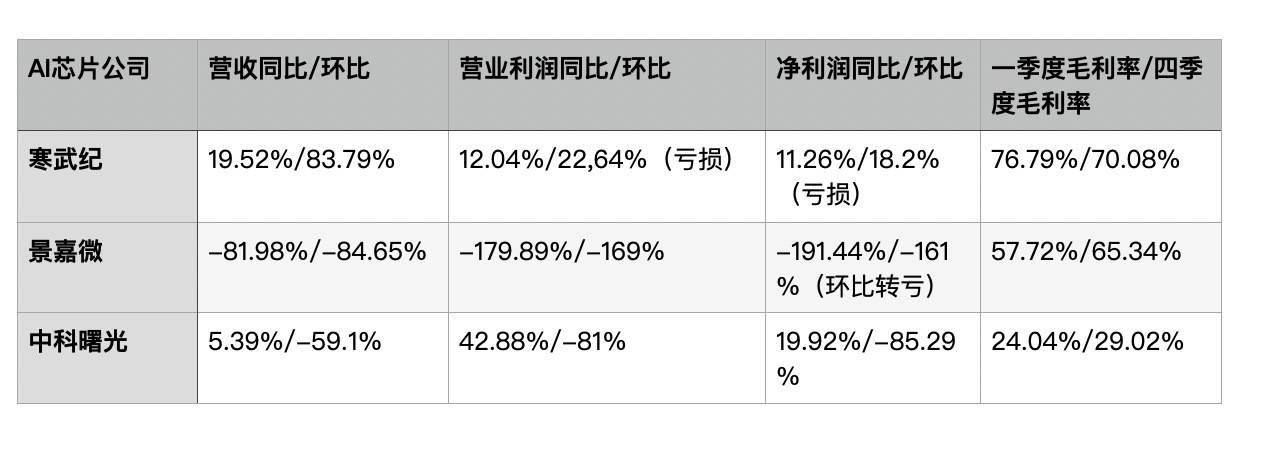

例如,Neolinear公司开发了用于模拟、RF和混合信号设计的EDA软件。NeoCircuit和 NeoCircuit-RF工具可以自动确定模拟、定制数字和RF电路的尺寸,这大大提高了设计工程师的生产率。NeoCell工具可以自动完成模拟单元的布局布线。在结合运用这些工具的情况下,Neolinear的技术可以实现快速模拟设计。表1给出了由Neolinear和台湾工业技术研究院 (ITR)共同完成的工作成果,它们证明了这种革命性的模拟综合技术可以实现的设计改进。表1的结果来自三个电路,分别是:

1. 跨导阻抗放大器,

2. 11位流水线型模数转换器的增益级,

3. 使用在3GHz PLL中的预分频器。

在全部的三种情况下,NeoCircuit工具都能够达到或超过手工设计电路的性能。

评论