带VCC输入引脚的硅序列码芯片DS2411及其应用

摘要:DS2411是Dallas Semiconductor公司推出的一种典型的一线式低成本电子识别码芯片。该器件带有外部电源输入引脚,可直接连接到微处理器的一个信号端口来进行高于15.4kbps速率的数据通信。文中介绍了DS2411的主要特点和引脚排列,重点给出了DS2411的应用设计方法。 关键词:一线器件;序列码;电子识别;DS2411 1 主要特点 DS2411硅序列码器件是MAXIM属下的Dallas Semiconductor公司推出的一种可使用外部电源的低成本电子识别码芯片。它能用最少的电子接口提供绝对唯一的电子身份标识(例如某种微控制器的一个信号端口引脚)。DS2411的注册码已经在工厂光刻进了64 Bit ROM,其中包括一个唯一的48 Bit序列号、一个8 Bit循环冗余校验码CRC和一个8 Bit家族码。数据可以通过Dallas Semiconductor公司的一线协议来进行连续传输。 在典型的一线设备中,要对器件的工作电压范围进行扩展,一般必须采用外部电源。而DS2411正是这样一种带有电源输出引脚的硅序列码芯片。该器件的主要特点如下: ● 唯一的、经过工厂激光刻制和检测的64 Bit注册码芯片(8 Bit家族码加48 Bit序列码加8 Bit CRC校验码);保证无重码;

本文引用地址:http://www.eepw.com.cn/article/201610/307547.htm

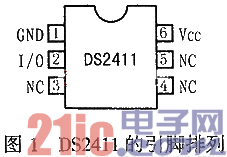

● 待机电流1μA; ● 内置多点控制器,可在一个一线网络中使用多个DS2411; ● 可与其它一线产品多点兼容; ● 一线主机可通过8 Bit家族码来识别连接到总线上的DS2411器件; ● 可直接连接到微处理器的一个信号端口,并以高于15.4kbps的速率进行通信 ● 在高速(Override)模式时通信速率可提升到125kbps ● 工作范围:1.5V~5.25V;-40℃~+85℃。 2 引脚功能和主要参数 DS2411采用TSOC、SOT23-3和Flip-Chip表面贴等封装形式。图1是其采用6脚TSOC封装的引脚排列图。 DS2411芯片的I/O和VCC端口到地之间的电压范围为-0.5V~+6V,I/O和VCC的电流最大值均为%26;#177;20mA。芯片的工作温度范围为-40%26;#176;C~+85%26;#176;C,最高结温为150%26;#176;C。 3 DS2411的应用设计 DS2411的注册码可通过单数据线进行访问。利用Dallas的一线协议可以获得这48 Bit序列码、8 Bit家族码和8 Bit CRC码。1-Wire协议根据特定时隙中总线的状态来工作,这些特定时隙始于总线主机发出的同步脉冲的下降沿。所有数据的读写均从最低位开始。从电源VCC上电到一线通信开始大约需要1200μs的延时,设备可以利用这段延时来发送检测脉冲。

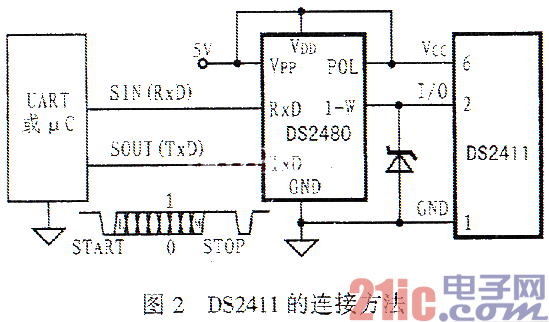

一线总线一般有一个单总线主机以及一个或多个从器件组成。DS2411在任何情况下都是从器件。通常总线主机件既可选用一个微控制器,也可选用Dallas Semiconductor公司的专用芯片(如DS2480、 DS2490或DS1481等)。一个一线总线系统一般需要考虑硬件配置、传输顺序和一线信令(包括信号类型和信号时序)等。 一线总线只有一根I/O数据线。总线上的每一个设备均会在需要的时间来驱动 I/O。正是由于这一点,接到1-Wire总线上的每个从器件的输出必须为漏极开路或三态输出。使用时,如果总线主机没有双向引脚,可把两个单独的输出和输入引脚连在一起来使用。同时在总线的主机端通常需要在总线上接一个上拉电阻,其连接方法如图2所示。一个多节点总线一般由一个一线总线和多个附属从器件组成。一线总线的标准数据速率可以达到15.4kbps,高速网络中则可达到125kbps。 一线总线的空闲状态为高电平。如果因为某种原因需要使传输暂时停止,并在其后使传输再次恢复,那么I/O应保持高电平。而如果总线电平被拉低,那么总线上的从器件会根据低电平的持续时间不同来把低电平当作一个时隙,或当作一个复位脉冲。 (1) 传输顺序 通过一线总线访问DS2411时,首先应当进行初始化,然后确定ROM功能命令,之后才能读数据。 一线总线上的所有传输操作均以初始化序列开始。初始化序列由总线主机发送的复位脉冲和随后从器件发送的一个在线应答脉冲组成。从器件发出的在线应答脉冲的作用主要是使总线主机能够知道DS2411已在总线上并已经作好操作准备。一旦总线主机检测到从器件的在线应答脉冲,它将发出一个读ROM、查询ROM或者过驱动跳跃ROM功能命令。所有功能命令码的长度均为1 byte。 图3 (2) 工作时序 DS2411需要遵循严格的协议,这样才能保证数据的完整。该协议中包含了四种类型的1-wire信号:由复位脉冲和应答脉冲组成的复位序列、写0、写1和读数据信号。除了应答脉冲之外,所有其它信号都由总线主机发出。DS2411可以采用两种速率进行通信:标准速率和高速模式。如果没有明确采用高速模式,DS2411将按照标准速率进行通信。 要把系统从空闲状态激活,1-wire总线上的线电压应当从VPUP降至阀值电压VTL以下。而要使系统从激活状态转换到空闲状态,其1-wire总线上的线电压则应从VILMAX 升至阀值电压VTH以上。系统逻辑电平的确定与DS2411的VILMAX电压有关,但该电压并不触发任何事件。 图3给出了启动一次通信所需要的初始化时序。复位脉冲之后的应答脉冲表示DS2411已经准备好接收数据,可以发送正确的ROM码和存储功能命令。在由多种从器件组成的多点网络中,复位脉冲为低的时间tRSTL应足够长,以保证最慢的1-wire从器件能够确认复位脉冲。如果总线主机在下降沿采用slew-rate控制方式,那么它必须将总线电压下拉并持续tRSTL+tF,以对该下降沿进行补偿。如果tRSTL的持续时间为480μs或更长,器件将从高速模式恢复为标准速率。如果DS2411处于高速模式且tRSTL小于80μs,那么器件将继续保持高速模式。 总线主机释放数据线并进入接收模式(RX)后, 1-wire总线将由上拉电阻拉至VPUP,采用DS2480B时电平的上拉是由其有源电路来实现的。当总线电压超过阀值VTH以后,DS2411会在等待tPDH之后,通过将总线拉低tPDL来发出一个应答脉冲。为检测应答脉冲,主机应在tMSP时刻对1-wire总线的逻辑状态进行检测。 tRSTH 的持续时间至少应该是tPDHMAX、 tPDLMAX和tRECMIN之和。一过tRSTH,DS2411马上就做好了接收数据的准备。在多种从器件组成的多点网络中,标准速率下tRSTH的持续时间至少应为480μs,高速模式下,tRSTH的持续时间至少应为48μs才能适应其它1-wire器件 。 与DS2411的数据通信是通过一个个时隙完成的,每个时隙只能传送一位数据。图4所示是其读写时隙图。通过写时隙可把数据从主机传送给从机,通过读时隙可把数据由从器件传送给主机。所有通信均以主机拉低数据线开始。当1-wire数据线上的电压降到阀值VTL以下时,DS2411将启动它内部的定时信号发生器,以决定在写时隙期间何时对数据线进行采样,同时确定读时隙期间数据保持有效所持续的时间。 图4 (3) 主机到从机的数据传输 对于写1时隙来说,当写1为低的时间tW1LMAX结束以后,数据线上的电压必须超过阀值VTHMAX;对于写0时隙来说,当写0为低的时间tW0LMIN结束以前,数据线上的电压则必须保持在阀值VTHMIN以下;为了最大限度地保证通信的可靠性,数据线上的电压在整个tW0L持续时间内不能超过 VILMAX。当数据线上电压超过阀值VTHMAX后,DS2411需要一个恢复时间tREC以便准备下一个时隙。 (4) 从机到主机的数据传输 读数据时隙的起始部分与写1时隙类似。在读信号为低的时间tRL结束以前,数据线上的电压必须保持在 VTLMIN 电压以下。在tRL期间,如果应答信号为0,DS2411便开始将数据线拉低;终止该下拉和使电压再次升高的时间可由内部定时信号发生器来确定。而如果应答信号为1,则DS2411就不再需要将数据线拉低,总线电压会在tRL结束后立即开始上升。 主机在数据线上执行一次读数采样所需的时间(tMSRMAX到tMSRMIN)一方面可由时序中的tRL+(上升时间)决定,另一方面可由DS2411内部的定时信号发生器决定。为了最大限度地保证通信的可靠性,tRL的持续时间在允许的范围内应当尽可能的短一些,同时主机的读取时间也应尽量靠近tMSRMAX但不能迟于tMSRMA。在从数据线上读数之后,主机还应当等到tSLOT结束后才开始下一个动作,以保证DS2411有足够的恢复时间tREC来准备下一个时隙。

评论