详述DRAM、SDRAM及DDR SDRAM的概念

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

本文引用地址:http://www.eepw.com.cn/article/201610/307439.htmDRAM

DRAM较其它内存类型的一个优势是它能够以IC(集成电路)上每个内存单元更少的电路实现。DRAM 的内存单元基于电容器上贮存的电荷。典型的DRAM 单元使用一个电容器及一个或三个FET(场效应晶体管)制成。典型的SRAM (静态随机访问内存)内存单元采取六个FET 器件,降低了相同尺寸时每个IC 的内存单元数量。与DRAM 相比,SRAM 使用起来更简便,接口更容易,数据访问时间更快。

DRAM核心结构由多个内存单元组成,这些内存单元分成由行和列组成的两维阵列(参见图1)。访问内存单元需要两步。先寻找某个行的地址,然后在选定行中寻找特定列的地址。换句话说,先在DRAM IC 内部读取整个行,然后列地址选择DRAM IC I/O(输入/ 输出)针脚要读取或要写入该行的哪一列。

DRAM读取具有破坏性,也就是说,在读操作中会破坏内存单元行中的数据。因此,必需在该行上的读或写操作结束时,把行数据写回到同一行中。这一操作称为预充电,是行上的最后一项操作。必须完成这一操作之后,才能访问新的行,这一操作称为关闭打开的行。

对计算机内存访问进行分析后表明,内存访问中最常用的类型是读取顺序的内存地址。这是合理的,因为读取计算机指令一般要比数据读取或写入更加常用。此外,大多数指令读取在内存中顺序进行,直到发生到指令分支或跳到子例程。

图1. DRAMs 内存单元分成由行和列组成的两维阵列。

DRAM的一个行称为内存页面,一旦打开行,您可以访问该行中多个顺序的或不同的列地址。这提高了内存访问速度,降低了内存时延,因为在访问同一个内存页面中的内存单元时,其不必把行地址重新发送给DRAM。结果,行地址是计算机的高阶地址位,列地址是低阶地址位。由于行地址和列地址在不同的时间发送,因此行地址和列地址复用到相同的DRAM 针脚上,以降低封装针脚数量、成本和尺寸。一般来说,行地址尺寸要大于列地址,因为使用的功率与列数有关。

早期的RAM拥有控制信号,如RAS# (行地址选择低有效)和CAS# (列地址选择低有效),选择执行的行和列寻址操作。其它DRAM 控制信号包括用来选择写入或读取操作的WE# (写启动低有效)、用来选择DRAM的CS#(芯片选择低有效)及OE# (输出启动低有效)。早期的DRAM拥有异步控制信号,并有各种定时规范,涵盖了其顺序和时间关系,来确定DRAM 工作模式。

早期的DRAM读取周期有四个步骤。第一步,RAS# 与地址总线上的行地址变低。第二步,CAS# 与地址总线上的列地址变低。第三步,OE#变低,读取数据出现在DQ 数据针脚上。在DQ 针脚上提供数据时,从第一步第三步的时间称为时延。最后一步是RAS#, CAS# 和OE# 变高(不活动),等待内部预充电操作在破坏性读取后完成行数据的恢复工作。从第一步开始到最后一步结束的时间是内存周期时间。上述信号的信号定时与边沿顺序有关,是异步的。这些早期DRAM没有同步时钟操作。

DRAM 内存单元必需刷新,避免丢失数据内容。这要求丢失电荷前刷新电容器。刷新内存由内存控制器负责,刷新时间指标因不同DRAM内存而不同。内存控制器对行地址进行仅RAS# 循环,进行刷新。在仅RAS# 循环结束时,进行预充电操作,恢复仅RAS# 循环中寻址的行数据。一般来说,内存控制器有一个行计数器,其顺序生成仅RAS# 刷新周期所需的所有行地址。

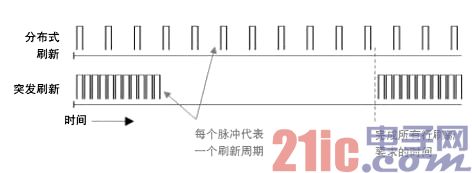

刷新策略有两个(参见图2)。第一个策略内存控制器在刷新周期突发中顺序刷新所有行,然后把内存控制返回处理器,以进行正常操作。在到达最大刷新时间前,会发生下一个刷新操作突发。第二个刷新策略是内存控制器使用正常处理器内存操作隔行扫描刷新周期。这种刷新方法在最大刷新时间内展开刷新周期。

图2. DRAM 刷新实现方案包括分布式刷新和突发刷新。

早期的DRAM 演进及实现了DRAM IC 上的刷新计数器,处理顺序生成的行地址。在DRAM IC 内部,刷新计数器是复用器输入,控制着内存阵列行地址。另一个复用器输入来自外部地址输入针脚的行地址。这个内部刷新计数器不需要内存控制器中的外部刷新计数器电路。部分DRAM 在RAS# 周期前支持一个CAS#,以使用内部生成的行地址发起刷新周期。

SDRAM

在接口到同步处理器时,DRAM 的异步操作带来了许多设计挑战。

SDRAM (同步DRAM)是为把DRAM操作同步到计算机系统其余部分,而不需要根据CE# (芯片启动活动低)、RAS#、CAS#和WE#边沿转换顺序定义所有内存操作模式而设计的。

SDRAM增加了时钟信号和内存命令的概念。内存命令的类型取决于SDRAM 时钟上升沿上的CE#, RAS#,CAS# 和WE# 信号状态。产品资料根据CE#, RAS#,CAS# 和WE# 信号状态,以表格形式描述内存命令。

例如,Activate (激活)命令向SDRAM发送一个行地址,打开内存的一个行(页面)。然后是一个Deselect (反选)命令序列,在对列地址发送Read 或Write 命令前满足定时要求。一旦使用Activate命令打开内存的行(页面),那么可以在内存的该行(页面)上运行多个Read和Write命令。要求Precharge(预充电)命令,关闭该行,然后才能打开另一行。

表1. DDR SDRAM 数据速率和时钟速度。

DDR SDRAM

通过提高时钟速率、突发数据及每个时钟周期传送两个数据位(参见表1),DDR (双倍数据速率) SDRAM 提高了内存数据速率性能。DDR SDRAM 在一条读取命令或一条写入命令中突发多个内存位置。读取内存操作必需发送一条Activate 命令,后面跟着一条Read 命令。内存在时延后以每个时钟周期两个内存位置的数据速率应答由两个、四个或八个内存位置组成的突发。因此,从两个连续的时钟周期中读取四个内存位置,或把四个内存位置写入两个连续的时钟周期中。

DDR SDRAM 有多个内存条,提供多个隔行扫描的内存访问,从而提高内存带宽。内存条是一个内存阵列,两个内存条是两个内存阵列,四个内存条是四个内存阵列,依此类推(参见图3)。四个内存条要求两个位用于内存条地址(BA0 和BA1)。

图3. DDR SDRAM中多个内存条提高了访问灵活性,改善了性能。

例如,有四个内存条的DDR SDRAM的工作方式如下。首先,Activate命令在第一个内存条中打开一行。第二个Activate命令在第二个内存条中打开一行。现在,可以把Read 或Write 命令的任意组合发送到打开行的第一个内存条或第二个内存条。在内存条上的Read 和Write 操作结束时,Precharge 命令关闭行,内存条对Activate 命令准备就绪,可以打开一个新行。

注意,DDR SDRAM要求的功率与打开行的内存条数量有关。打开的行越多,要求的功率越高,行尺寸越大,要求的功率越高。因此,对低功率应用,一次在每个内存条中只应打开一行,而不是一次打开行的多个内存条。

在内存条地址位连接到内存系统中的低阶地址位时,支持隔行扫描连续内存条中的连续内存字。在内存条地址位连接到内存系统中的高阶地址时,连续内存字位于同一个内存条中。

DDR2 SDRAM

DDR2 SDRAM 较DDR SDRAM 有多处改进。DDR2SDRAM时钟速率更高,从而提高了内存数据速率(参见表2)。随着时钟速率提高,信号完整性对可靠运行内存变得越来越重要。随着时钟速率提高,电路板上的信号轨迹变成传输线,在信号线末端进行合理的布局和端接变得更加重要。

地址、时钟和命令信号的端接相对简明,因为这些信号是单向的,并端接在电路板上。数据信号和数据选通是双向的。内存控制器中心在写入操作中驱动这些信号,DDR2 SDRAM在读取操作中驱动这些信号。多个DDR2 SDRAM 连接到同一个数据信号和数据选通上,进一步提高了复杂度。多个DDR2 SDRAM 可以位于内存系统相同的DIMM上,也可以位于内存系统不同的DIMM上。结果,数据和数据选通驱动器和接收机不断变化,具体取决于读取/ 写入操作及访问的是哪个DDR2 SDRAM。

表2. DDR2 SDRAM 数据速率和时钟速度。

通过提供ODT (芯片内端接),并提供ODT 信号,实现片内端接,并能够使用DDR2 SDRAM 扩展模式寄存器对片内端接值编程(75 欧姆、150 欧姆等等),DDR2SDRAM 改善了信号完整性。

片内端接大小和操作由内存控制器中心控制,与DDR2SDRAM DIMM 的位置及内存操作类型(读取或写入)有关。通过为数据有效窗口创建更大的眼图,提高电压余量、提高转换速率、降低过冲、降低ISI (码间干扰),ODT操作改善了信号完整性。

DDR2 SDRAM 在1.8V 上操作,降低了内存系统的功率,这一功率是DDR SDRAM 的2.5V 功率的72%。在某些实现方案中,行中的列数已经下降,在激活行进行读取或写入时降低了功率。

降低工作电压的另一个优势是降低了逻辑电压摆幅。在转换速率相同时,电压摆幅下降会提高逻辑转换速度,支持更快的时钟速率。此外,数据选通可以编程为差分信号。使用差分数据选通信号降低了噪声、串扰、动态功耗和EMI (电磁干扰),提高了噪声余量。差分或单端数据选通操作配置有DDR2 SDRAM 扩展模式寄存器。

DDR2 SDRAM 引入的一种新功能是附加时延,它使得内存控制器中心能够在Activate命令后,更快地灵活发送Read 和Write 命令。这优化了内存吞吐量,通过使用DDR2 SDRAM扩展模式寄存器对附加时延编程来配置。DDR2 SDRAM使用八个内存条,改善了1Gb和2GbDDR2 SDRAM 的数据带宽。通过隔行扫描不同的内存条操作,八个内存条提高了访问大型内存D D R 2SDRAM的灵活性。此外,对大型内存,DDR2 SDRAM支持最多八个内存条的突发长度。

DDR3 SDRAM

DDR3 SDRAM 是一种性能演进版本,增强了SDRAM技术,它从800 Mb/s开始,这是大多数DDR2 SDRAM支持的最高数据速率。DDR3 SDRAM支持六档数据速率和时钟速度(参见表3)。DDR3-800/1066/1333SDRAM 于2007 年投入使用,DDR3-1600/1866SDRAM 则预计在2008 年投入使用,DDR3-2133SDRAM 则预计在2009 投入使用。

DDR3-1066 SDRAM的能耗低于DDR2-800 SDRAM,因为DDR3 SDRAM 的工作电压是1.5 V,是DDR2SDRAM 的83%,DDR2 SDRAM 的工作电压是1.8 伏。此外,DDR3 SDRAM数据DQ驱动器的阻抗是34欧姆,DDR2 SDRAM 的阻抗较低,是18 欧姆。

表3. 预计的DDR3 SDRAM 数据速率和时钟速度。

DDR3 SDRAM 将从512 Mb 内存开始,将来将发展到8 Gb 内存。与DDR2 SDRAM 一样,DDR3 SDRAM 数据输出配置包括x4、x8 和x16。DDR3 SDRAM 有8 个内存条,DDR2 SDRAM 则有4 个或8 个内存条,具体视内存大小而定。

DDR2 和DDR3 SDRAM 都有4 个模式寄存器。DDR2 定义了前两个模式寄存器,另两个模式寄存器则预留给将来使用。DDR3使用全部4个模式寄存器。一个重要差异是DDR2 模式寄存器规定了读出操作的CAS 时延,写入时延则是1减去模式寄存器读出时延设置。DDR3模式寄存器对CAS 读出时延和写入时延的设置是唯一的。

DDR3 SDRAM使用8n预取架构,在4个时钟周期中传送8 个数据字。DDR2 SDRAM 使用4n 预取架构,在2个时钟周期中传送4 个数据字。

DDR3 SDRAM 模式寄存器可以编程为支持飞行突变,这会把传送8个数据字缩短到传送4个数据字,这在读出或写入命令期间把地址行12 设为低来实现。飞行突变在概念上与DDR2 和DDR3 SDRAM 中地址行10 的读出和写入自动预充电功能类似。

值得一提的另一个DDR3 SDRAM属性是差分的数据选通信号DQS,DDR2 SDRAM数据通信号则可以由模式寄存器编程为单端或差分。DDR3 SDRAM 还有一个新引脚,这个引脚为活动低异步RESET# 引脚,通过把SDRAM 置于已知状态,而不管当前状态如何,改善系统稳定性。DDR3 SDRAM 使用的FBGA 封装类型与DDR2 SDRAM 相同。

DDR3 DIMM为DIMM上的命令、时钟和地址提供了端接。采用DDR2 DIMM 的内存系统端接主板上的命令、时钟和地址。DIMM上的DDR3 DIMM端接支持飞行拓扑,SDRAM 上的每个命令、时钟和地址引脚都连接到一条轨迹上,然后这条轨迹终结在DIMM的轨迹端。这改善了信号完整性,其运行速度要快于DDR2 DIMM树型结构。

飞行拓扑为内存控制器引入了新的DDR3 SDRAM写入电平功能,考虑了写入过程中时钟CK和数据选通信号DQS 之间的定时偏移。DDR3 DIMM 的主要不同于DDR2 DIMM,防止把错误的DIMM 插入主板中。

DDR4 SDRAM

DDR4 SDRAM 已经拉开帷幕,预计将在2012 年发布。其目标是在1.2V 或以下的电源上运行这些新存储器芯片,同时实现每秒200 万以上的数据传送速度。

GDDR 和LPDDR

其它DDR变种,如GDDR (图形DDR)和LPDDR (低功率DDR),在业内的地位也在不断提高。

GDDR是一种图形卡专用存储技术,目前规定的变种有四个:GDDR2、GDDR3、GDDR4 和GDDR5。GDDR的技术与传统DDR SDRAM 非常类似,但功率要求不同。其降低了功率要求,以简化冷却,提供更高性能的存储器模块。GDDR也是为更好地处理处理图形要求设计的。

LPDDR 采用166 MHz 时钟速率,在要求低功耗的便携式消费电子中正越来越流行。LPDDR2 改善了能源效率,其工作电压最低1.2V,时钟速度为100 -533 MHz。

评论