一种通用基于CPLD实现的CAN接口连接设计

摘要:介绍一种基于CPLD实现的DSP或ARM处理器与CAN总线控制器SJA1000接口连接设计。通常DSP或ARM处理器都有独立的地址和数据总线,而SJA1000采用的是地址、数据分时复用总线,它们不能直接连接。该设计主要是通过CPLD实现这两种总线方式的转接。该方案成本低,性能稳定,实现可靠。采用CPLD使该设计更为自由、灵活。在处理器与CPLD的连接一侧是采用微处理器用独立的地址和数据总线访问外部存储器的方式工作的,而许多具有独立的地址和数据总线的微处理器都能做到访问外部存储器,从而使该设计具有很强的通用性。全篇给出了完整详细的设计代码和仿真结果,并在实际应用中得到检验,可直接应用到设计中。

本文引用地址:http://www.eepw.com.cn/article/201609/304285.htm在工业自动化领域,CAN口通信以其卓越的性能、极高的可靠性和低廉的价格得到广范的应用。Philips公司的SJA1000芯片,是目前使用最为广泛的一种独立CAN总线控制器。SJA1000有一系列先进的功能,适合于多种应用,特别在系统优化,诊断和维护方面非常重要。

为了连接到主控制器,SJA1000提供一个分时复用的地址、数据总线和附加的读写控制信号。SJA1000可以作为主控制器外围存储器映射的I/O器件直接连接到具有Intel方式接口的主控制器。而目前大部分DSP和ARM处理器都是采用独立的地址和数据总线访问外部存储器的,由于时序不相兼容的原因,这些处理器不能直接访问SJA1000。从而设计一种转接电路使DSP和ARM处理器能够连接SJA1000变得很必要。本设计正是解决这一问题。

1 总体设计

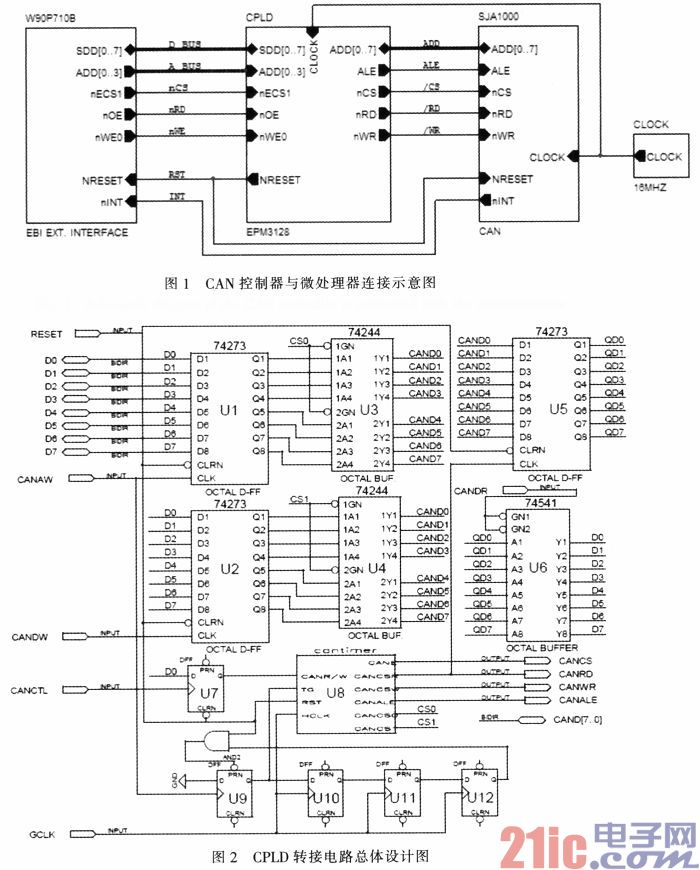

该设计以新塘科技生产的ARM7处理器W90P710B与SJA1000的连接为例,W90P710B采用独立的地址和数据总线访问外部存储器方式工作。图1表明了CPLD在W90P710B与SJA1000之间的这种转接关系。

设计中采用的CPLD选用Altera公司的MAX系列可编程逻辑器件EPM3128A芯片。EPM3128A具有128个宏单元,96用户I/O管脚数,2500个可用门,管脚间延迟快至10ns,计数器速度可高达100 MHz,可以很好的满足设计需要。本设计采用图形和AHDL语言混合输入完成。使用工具为MaxplusⅡ。Ateral公司的MaxplusⅡ,QuartusⅡ,也是业界最著名的CP LD/FPGA开发工具,支持所有的Ateral芯片,如MAX3000,MAX7000,MAX2Ⅱ系列。

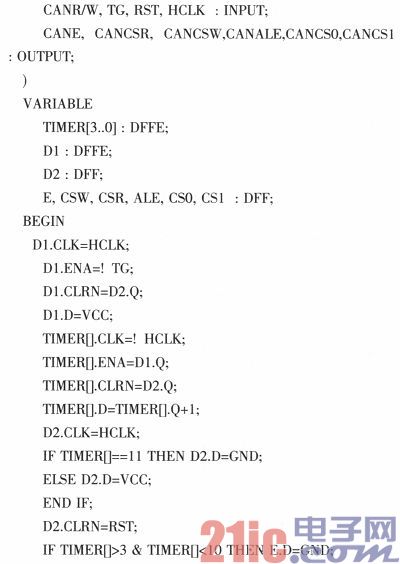

图2是转接电路总体设计图,与ARM处理器连接一侧,锁存器U1用于存储CAN控制器要访问的地址,U1的片选信号为CANAW,该信号同时起到启动时序电路U8输出读写时序的作用;锁存器U2用于存储要写入CAN控制器的数据,U2的片选是CANDW;锁存器U7的输出为高,控制U8输出读时序对CAN控制器读取数据,读出的数据存入U5中,锁存器U7的输出为低,控制U8输出写时序对CAN控制器SJA1000进行写操作,将U2中的数据写入U1所代表的,CAN所在地址中,其片选信号为CANCTL;门电路U6通过片选信号CANDR用以读取U5中存放的CAN读出数据。综上所知,CPLD与ARM处理器接口的是4个寄存器,它们分别是3个写寄存器:CAN地址写寄存器CANAW,CAN数据写寄存器CANDW,CAN控制寄存器CANCTL;一个读寄存器:CAN数据读CANDR。ARM就是通过这4个寄存器来操作SJA1000 CAN控制器的。

CPLD与SJA1000连接一侧是INTEL方式的标准信号CANCS、CANRD、CANWR、CANALE,这4个信号由时序电路U8产生。U3、U4的输出,U5的输入都与SJA1000的数据总线相连,用以接收地址和读写数据。

复位信号RESET使系统上电时处于初始状态。时钟信号GCLK取8 MHz,由SJA1000的16 MHz时种2分频得来。U9-U12用以延宽CANAW对U8的低电平启动脉冲,使U8工作的更可靠。整个设计占用ARM4个地址和一个中断资源,只要有足够的地址和中断源ARM就可按此设计扩充出多个CAN口。

2 时序电路设计

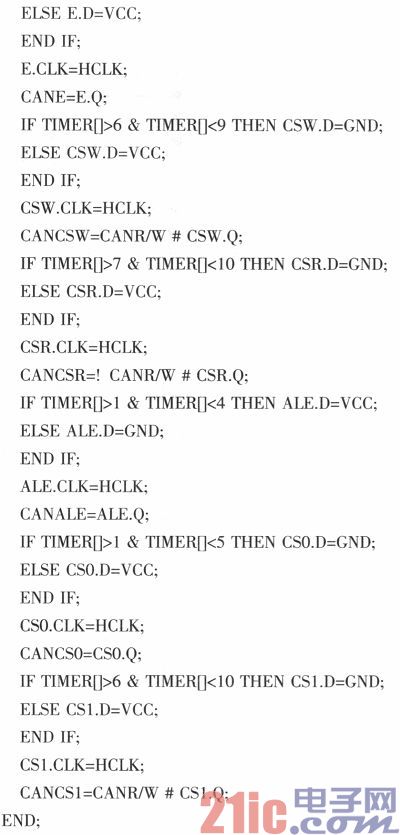

CAN读写时序电路U8的设计输入采用AHDL语言,其电路符号如图3所示。

U8的设计代码如下:

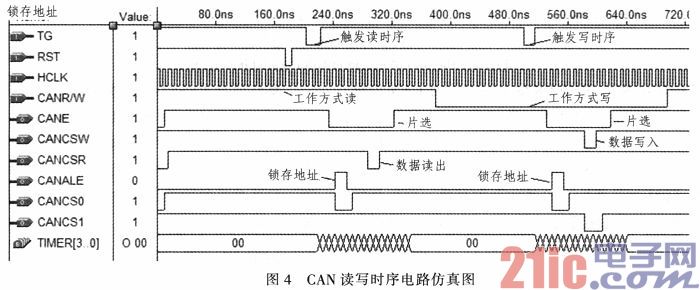

其波形仿真结果如图4所示。

3 转接电路工作原理介绍

CAN读写时序电路U8是整个设计的核心,它起到对SJA1000进行读写操作的作用。

当ARM处理器要对SJA1000进行读操作时,它先通过CANCTL片选在U7中写入‘1’高电平,使U8工作在读的状态,然后把要读的地址通过片选CANAW写入U1,片选CANAW还启动了U8的TG触发信号(图4的前半部分、CANE为低与CANR/W为高的那部分),使U8的CANE(即CANCS)输出低电平,CANCS0输出低脉冲打开门电路U3,使CAN地址出现在SJA1000的总线上,同时CANALE出现一个正脉冲,将该地址锁存到SJA1000的地址寄存器中,随后CANCSR(即CANRD)输出低电平对SJA1000进行读数据,在CANCSR低电平脉冲结束的上升沿处出现SJA1000总线上的数据被锁存到U5寄存器中,然后CANE变高,读时序完成。随后ARM处理器通过CANDR片选打开门U6将数据读走。

当ARM处理器要对SJA1000进行写操作时,它先通过CANCTL片选在U7中写入‘0’低电平,使U8工作在写的状态,然后再把要写的数据通过片选CANDW写入U2,最后把要写的地址通过片选CANAW写入U1,片选CANAW还启动了U8的TG触发信号(图4的后半部分、CANE与CANR/W同时为低的那部分),使U8的CANE(即CANCS)输出低电平,CANCS0输出低脉冲打开门电路U3,使CAN地址出现在SJA1000的总线上,同时CANALE出现一个正脉冲,将该地址锁存到SJA1000的地址寄存器中,随后CANCS1输出低脉冲打开门电路U4,使CAN要写入的数据出现在SJA1000的总线上,同时CANCSW(即CANWR)输出低电平对SJA1000进行数据写入,然后CANE变高,写时序完成。

评论