用Spartan-3A DSP器件实现汽车应用中的块匹配

汽车工程师采用多种智能技术帮助人们安全驾驶汽车。汽车系统中的主要技术包括雷达、超声和摄像/视觉感测。这些技术统称驾驶员辅助 (DA) 系统,用于在恶劣条件和危险路况下协助安全驾驶。

本文引用地址:http://www.eepw.com.cn/article/196660.htm第一代摄像 DA 系统目前可见于各种生产用车型。这类系统大多为驾驶员提供车辆周边环境的视频图像。最常见的是泊车/倒车辅助系统,这种系统用后视摄像头拍摄本车后面的景物,并且在无线电/导航系统的屏幕上或者在仪表板中的小型显示器上显示图像。

第二代摄像系统正处于开发测试阶段,目前使用有限。第二代系统并非仅为驾驶员提供图像,而是运用图像处理与解析从视频流中提取信息,并且对车辆环境进行表征和评估。必要时驾驶员会收到相应警示。

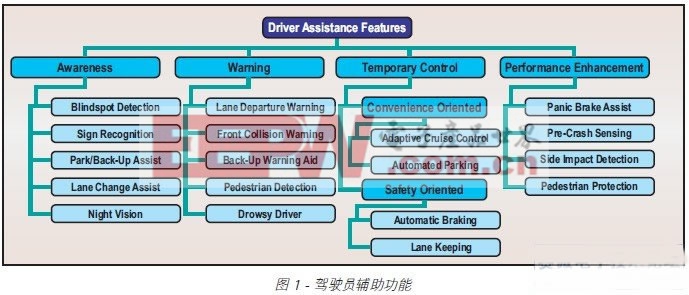

随着工程师们获取车辆环境表征方面的实际经验,未来的 DA 技术会更复杂,将为消费者提供更强大的实用工具并且增强其他汽车子系统的性能。图 1 概括了目前和未来的多种 DA 功能。

高级处理要求

DA 系统的处理要求可能超过目前汽车级串行 DSP 处理器的能力。另外,为了提高消费价值,在一套视觉传感器上捆绑多种 DA 功能的需求日益高涨。

例如,前瞻视觉模块可能需要同时支持车道偏离警示、智能大灯控制和标志识别功能,而所有这些都需要不同的处理算法。因此,对于用 FPGA 通过原始图像数据处理、配置灵活性和器件可缩放性来提供系统价值,DA 市场提供了实实在在的机会。

视觉 DA 系统的图像处理与解析功能可以包括空间/时间滤波、镜头失真校正、图像清晰化、对比度增强、边沿检测、图像匹配、物体识别和物体跟踪,在某些情况下还包括图形叠加。尤其值得关注的是一种支持运动估计或立体视差计算的图像匹配功能。

为了说明 FPGA 处理的性能价值,我们来考虑这样一个视觉系统:以 30 Hz 帧速率 (fps) 生成视频的宽幅 VGA 分辨率成像器件(752×480 像素),而且需要估计帧间物体运动(或流动)。有一种算法(也适用于立体视差计算)是将图像划分为若干个块(如大小为 4×4 像素),然后判断第一帧中各图像块对第二帧中指定搜索区(如 20×20 像素)内某位置的匹配条件。

一种常用的匹配条件是用算子 SAD(绝对差和)求出第一帧图像中的 4×4 块与第二帧图像上搜索区内的像素之间的像素灰度最小绝对误差 (MAE)。

我们的 4×4 块匹配示例需要 250 MMAE/s(每秒百万次 MAE 计算)以上的性能,因为 (752 像素)×(480 行)×(20 ×20 像素搜索区)×(30 fps)/(4×4 像素块大小) = 270,720,000 MAE/s。MAE 表示 4×4 像素块的最终匹配误差,而 SAD 是指根据四个独立元素对进行计算得到的绝对差和。所以,每 MAE 需要四次 SAD 运算。

处理选项

由汽车设计工程师决定的处理选项包括超长指令字 (VLIW) DSP-CPU 和 FPGA。FPGA 的处理能力远远高于任何现有的 VLIW DSP-CPU。这是由于 FPGA 的架构:大量并行功能单元(包括可编程 MAC)使 FPGA 的性能比任何 DSP 都高出 10-30 倍(具体性能取决于所实现的应用),即使 FPGA 的时钟频率比 DSP-CPU 的时钟频率低得多。我们使用块匹配运算示例,是要证明 Xilinx® FPGA 的性能比任何 VLIW DSP-CPU 处理器都高。

VLIW DSP-CPU 处理器中的 SAD 和 MAE 计算

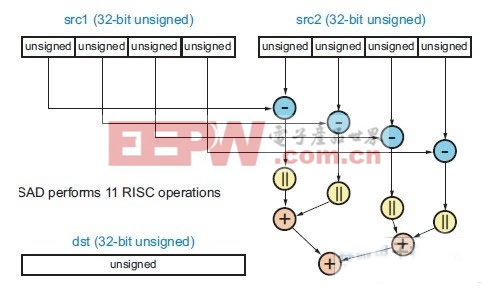

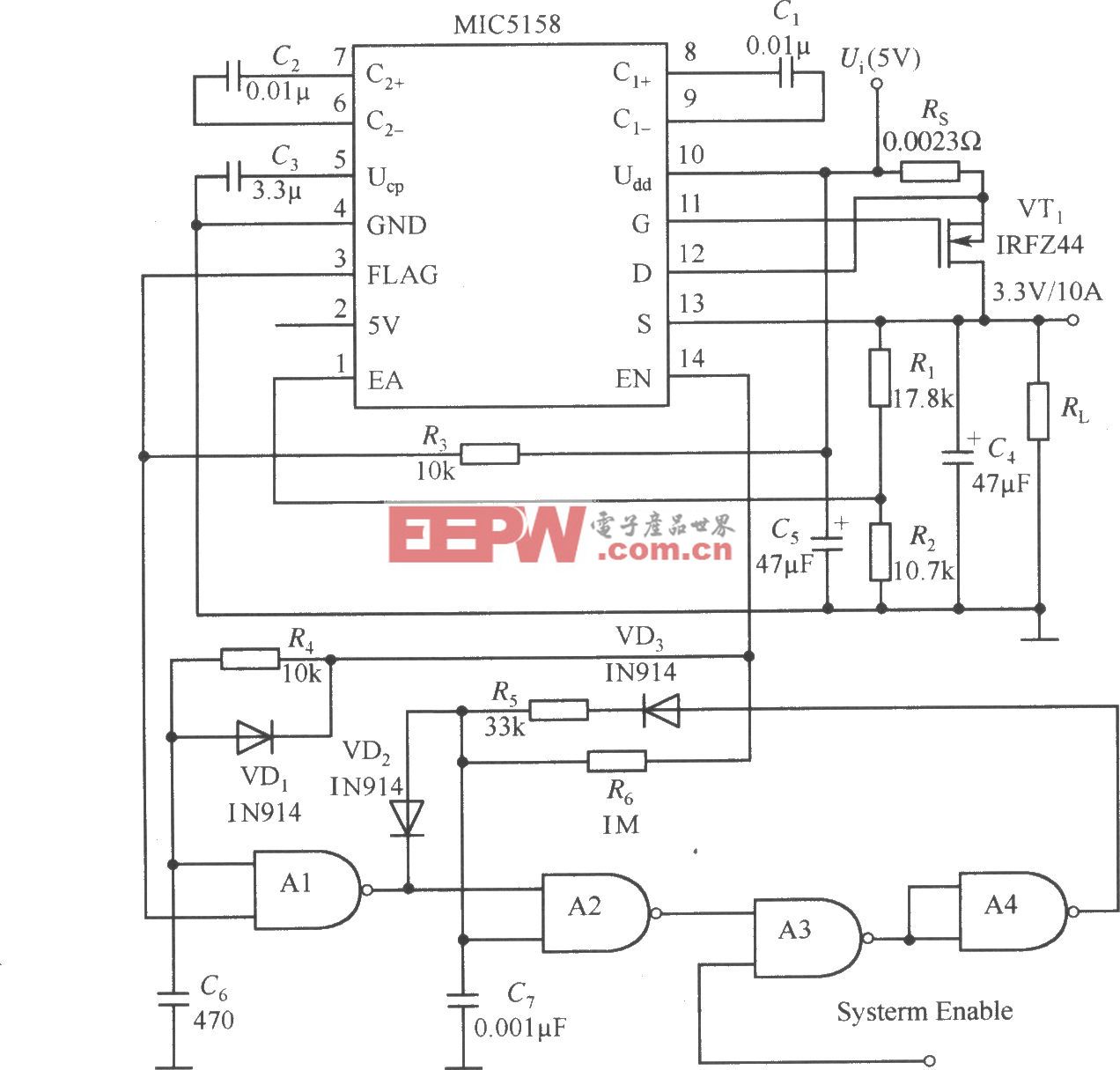

在一个 32 位架构的单指令多数据 (SIMD) DSP-CPU 中可实现四个 8 位像素视频数据单元的 SAD 运算,因此,仅在一个周期内即可有效执行相当于 11 条基本指令的运算,如图2 所示。

图2

例如,Nexperia PNX1500 媒体处理器配有 32 位 TriMedia VLIW-CPU,对于具有二周期延迟的 8 位像素,可以在一个时钟周期内执行两条四路 SAD 指令。算上超长指令字,就是每时钟周期最多五条基本 RISC/SIMD 指令,其中只有两条可以是 SAD 指令(在 TriMedia 数据手册中称为“8meii”)。

所以,对 4×4 大小的块进行 MAE 计算需要五个时钟周期,如表 1 所示:两个周期用于两条四路 SAD 指令的流水线处理(周期 1 用于 sad1/sad2,周期 2 用于 sad3/sad4);三个周期用于部分结果的累加(周期3、4 和 5)。因此,如果只处理一个块,则一个 300 MHz 的 Nexperia PNX1500 处理器的处理能力最高可达 60 MMAE/s。

如果每次处理一个以上 4×4 块,最高性能可略有提高。例如,可以在七个周期内计算两个并行 4×4 块的 MAE,这时性能可达 85.71 MMAE/s;而处理三个块需要九个周期,即性能为 100 MMAE/s。

可并行处理的最大块数分别受限于任意长指令字中允许的 SIMD SAD 运算次数、VLIW-CPU 的通用寄存器数和优化编译器的调度算法。如果继续增加块数,整体性能会趋于饱和,因此我们考虑并行处理的 MAE 不超过三个。

德州仪器 (TI) 的 TMSD320DM6437 数字媒体处理器每周期有一条由八次基本 RISC 运算组成的长指令,分别通过两条数据通路,各通路每周期有四个时隙。其 VLIW-CPU 每周期最多可执行两条 SAD 指令(在 TI DM6437 数据手册中称为“subabs4”),各指令有一个周期的延迟。但是,要累加部分结果,就必须使用常数 0x01010101 执行具有三周期延迟的 SIMD MAC 运算(称为“dotpsu4”)。

所以,600 MHz 的 TI DM6437 DSP-CPU 可以用七个周期计算一个 MAE(如表 2 所示),因此对于 4 x 4 像素块的最高性能为 85.71 MMAE/s。如果并行处理两个块,就需要九个周期,性能为 133.33 MMAE/s;而三个块需要 11 个周期,性能为 163.64 MMAE/s,这仍然低于我们的 250 MSAD/s 要求。

VLIW DSP-CPU 性能不足

至此,我们一直假定每像素 8 位,这很适合 32 位架构的 DSP-CPU 处理器。然而,新型 CMOS 图像传感器的分辨率范围较高,即每像素 12 到 14 位。对于这些数据类型,32 位架构的传统四路 8 位子字 SIMD 不够有效,必须换用双路 16 位半字 SIMD,其中的子字并行度仅为二。因此,由于计算一个 MAE 需要较多时钟周期,最高性能大幅度下降。

表3 所示为在 TI VLIW DSP-CPU 上使用 16 位子字指令计算 SAD 时可能的伪汇编代码,假定延迟正确且函数发射时隙允许执行这种指令。因此,一个 4×4 的块需要八个周期,而并行处理两个和三个块分别需要 10 个和 12 个周期。这时,相应的最高性能分别为 75 MMAE/s、120 MMAE/s 和 150 MMAE/s。这些数字都比使用 8 位子字指令得到的数字小。

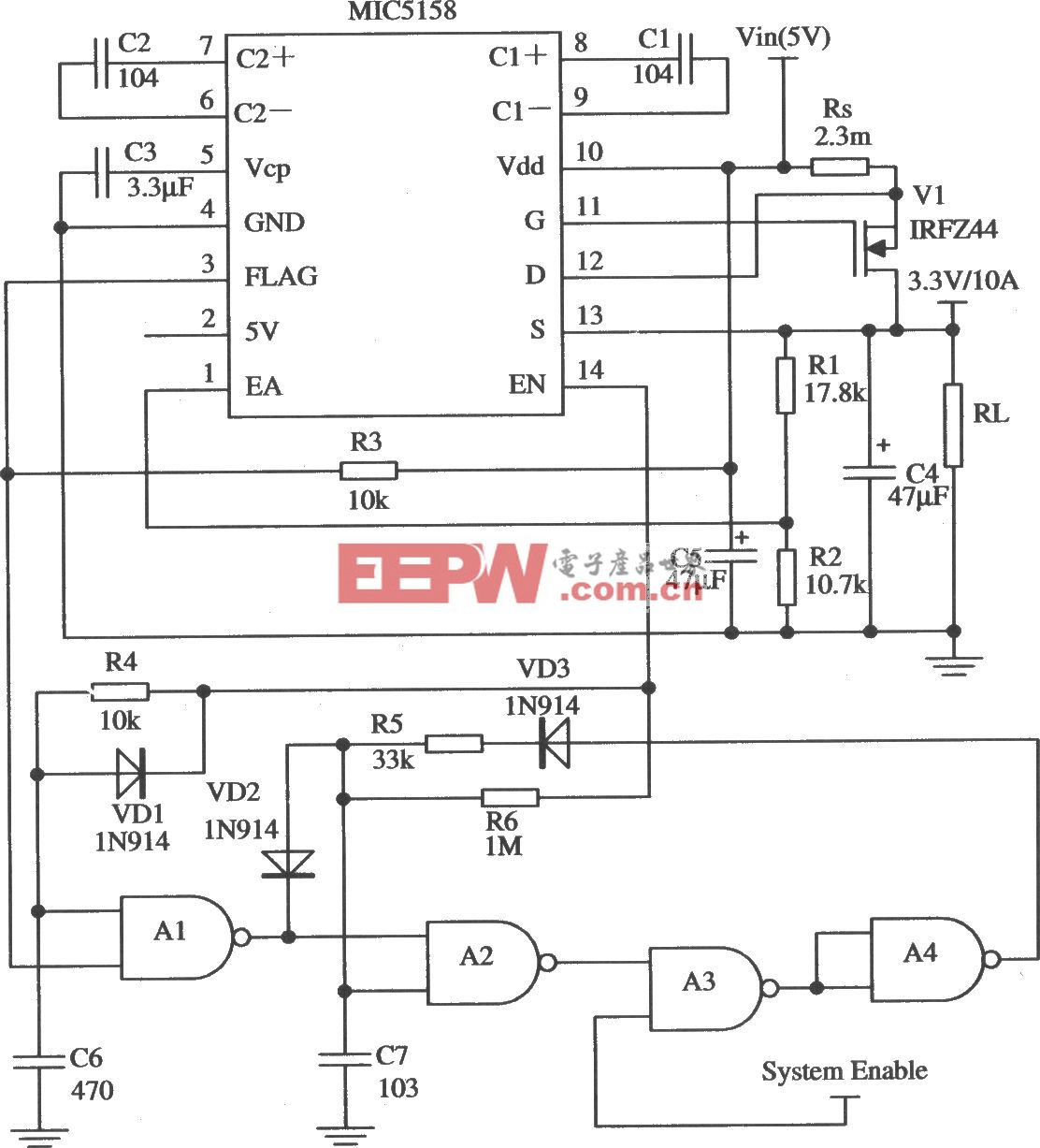

Spartan-3A DSP FPGA 的 SAD 和 MAE 性能

为了填补 Spartan™-3 和 Virtex™-4 器件之间的处理性能空白,Xilinx 推出了 Spartan 3A-DSP 1800A 和 3400A FPGA。这些器件采纳了 Virtex-4 器件中的 DSP48 Slice 的修改版。另外,3A-DSP 器件包括大量片上存储器(Block RAM)。这两方面增强加上针对大量应用制订的价位使 3A-DSP 器件非常适合汽车视觉 DA 系统。

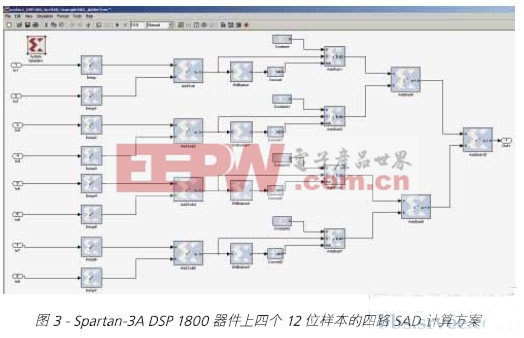

图 3 所示为 Spartan-3A DSP 1800 (XC3SD1800A-4FG676) 器件上的四路 12 位像素的 SAD 计算方案。此实现是使用 System Generator for DSP 设计流程(Xilinx 提供的 Simulink 工具中的数位和周期都精确的可综合库)完成的。所需资源数量是 121 个 Slice(236 个 LUT 和 140 个触发器)。将此结构复制四次并且加上部分结果,即得到整个 4×4 块的计算方案,该方案需要 508 个 Slice(990 个触发器和 606 个 LUT),具有一个周期吞吐量(这意味着可从任意时钟周期开始计算新的 MAE)和七个周期延迟。

如果使用 150 MHz 时钟频率(该器件最高时钟频率为 250 MHz),只需要两个并行结构(约占器件面积的 6%)即可达到 300 MMAE/s 的性能,从而满足示例应用的 250 MMAE/s 性能要求。这样可以节省大量资源用来实现其他图像处理功能、数据路由管道、存储器接口控制器以及一个用于串行处理和外部通信的 32 位 MicroBlaze™ 嵌入式处理器。

作为参考,仍然用 150 MHz 频率,Spartan 3A-DSP 1800A 器件仅使用整个 FPGA 器件的 70% 即可并行处理多达 23 个块(70%×16,640 Slice/508 Slice/块 = 23 块)。与此对应的最高性能是 3,529 MMAE/s,这至少要比 600 MHz 的 TI DSP-CPU 的最高性能高 25 倍。

结论

我们以汽车视觉应用为例说明了如何利用中型低成本 Xilinx FPGA 的可编程并行处理能力提供超过 VLIW DSP-CPU 的处理性能。表 4 列出了我们的分析结果。

请注意,对于 12 位像素数据的 4 x 4 块的 MAE 计算,Spartan-3A DSP 的性能仅以四分之一时钟速度即可达到 TI TMS320DM6437 的两倍。另外,FPGA 的资源占用率仅为 6%,因此可以在同一器件上实现其他图像处理功能(必要时可采纳并行处理)。

另一方面,VLIW DSP-CPU 在 SAD 计算期间被完全占用,消耗串行处理器长指令的可用时隙,因此很少有机会同时执行其他功能。

我们对于 FPGA 的估算时钟频率相当保守(以 150 MHz 对 250 MHz),对于运动估算的搜索区也是如此(搜索区越大,需要计算的 MAE 的数量就越多)。例如,30×30 的搜索区需要 609 MMAE/s 的性能(远远超过 VLIW DSP-CPU 的能力),然而却仅占用 1800A 器件上 Slice 的 12%。

最后,我们在实现 MAE 时根本未使用 DSP48 MAC 单元:据我们估计,如果用四个 DSP48 单元取代由 100 个 Slice 组成的加法器树,则一个 12 位输入数据 MAE 的 4×4 块会占用 400 个 Slice(782 个触发器和 400 个 LUT)和四个 DSP48。

因此,Spartan-3A DSP 1800A 器件非常适合需要极高处理性能、灵活性和可缩放性的视觉应用,如未来型汽车驾驶员辅助系统中的视觉应用。

评论