多通道同步数据采集及压缩系统

1 引言

现代遥测系统中为了尽可能少地占用传输时间和存储空间,在有限的信道容量内传输更多的有用信息,采用数据压缩技术,有助于降低功率和带宽要求,改善通信效率。这里提出一种基于DSP与CPLD的多通道同步数据采集与压缩系统设计方案,该系统应用于遥测多路噪声数据,其中多通道同步数据采集可实现同时测量信号。并进行相关分析后,得到信号间的相关信息,而DSP内嵌的数据压缩算法实现其数据压缩的功能。

2 系统的硬件结构

2.1 系统设计思路

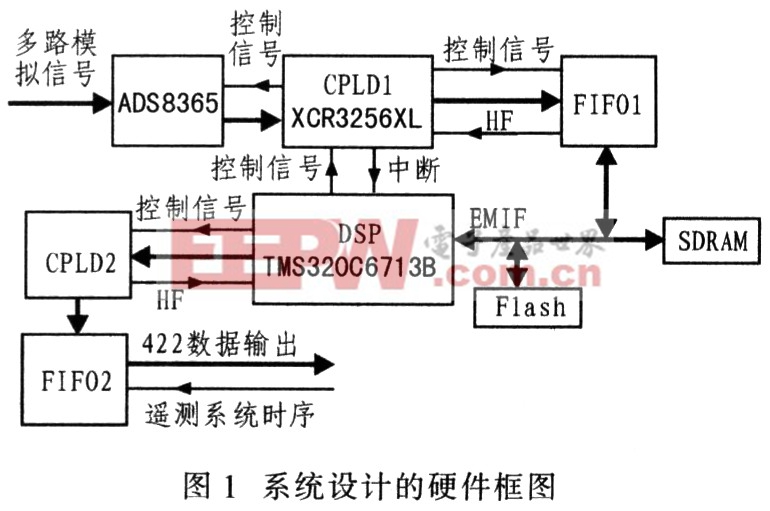

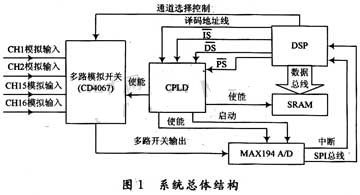

图1为系统设计的硬件框图。基于CPLD和DSP的多通道同步数据采集及压缩系统主要由数据采集模块、数据处理模块以及数据接口模块3部分构成。前端由传感器输人的模拟信号经信号调理模块的整形放大后,输入到 A/D转换模块中,模拟量转变为数字量,可编程逻辑器件(CPLD1)控制A/D转换器,按照设定的采样率采集数据,将采集到的数据通过总线写入 FIFO,FIFO半满时.发送一次半满信号,即DSP的中断,DSP接收到中断后立即将一帧数据从FIFO中读人到数据处理模块。DSP将其采集的数据高速压缩后写入到接口模块,再由可编程逻辑器件(CPLD2)通过RS-422总线将数据传送至遥测系统,做进一步分析。

2.2 器件选型

2.2.1 A/D转换器ADS8365

该系统的A/D转换模块选用TI公司的 ADS8365型A/D转换器,该件支持6通道信号差分输入,有3组信号采集控制端,每组控制2路信号,16位精度,每通道的转换速度高达250 kHz。支持高速并行数据输出接口,数据输出接口包括直接地址选择模式、CYCLE模式、FIFO模式。

2.2.2 复杂可变程逻辑器件(CPLD)XCR3256XL

采用CPLD控制各个接口,这里选用 XCR3256XL型CPLD,它是Xilinx公司的CoolRunner系列的高性能复杂可编程逻辑器件(CPLD)。该器件具有如下特点:采用 COMSEEPROM制造工艺技术;内置标准JTAG接口,支持3.3 V在系统可编程(ISP);3.3 V电源,集成密度为6 000个可用门;引脚间延时7.5 ns.系统频率高达140 MHz。同分离逻辑器件相比,单片CPLD实现逻辑控制功能,简化电路设计,提高系统可靠性。另外,XCR3256XL具有在系统可编程的功能,只需一根下载电缆连接至目标板上,可方便实现多次重复编程,大大方便电路调试。

2.2.3 数字信号处理器(DSP)TMS320C6713B

该系统设计的DSP选用TMS320C6713B,该器件TI公司推出的TMS320C67xx系列浮点DSP中的一款。它采用改进型哈佛结构,具有运算速度快、功耗小和性价比高等特点。其体系结构采用 Veloci TI超长指令字VLIW(Very Long Instruction Word)结构。每周期执行8条32位指令,支持32/64位数据。采用类RISC指令集,具有300 MHz、3.3 ns指令周期的运行速度和2 400 MI/s或1 800 MFLOPS的处理能力适用于高速信号处理。为了加快处理速度,DSP内核采用2级CACHE,其中L1级CACHE分为4 KB直接程序CACHE和4 KB数据CACHE(分为2路);L2级CACHE分为64 KB统一存储器和192 KB附加存储器。其内部有16通道EDMA控制器,能够高速处理几乎所有I/O和存储器的接口问题,大大提高器件吞吐速度。外部总的存储器地址空间最大 512MB,数据宽度为32 b,可支持SBRAM,SDRAM,SRAM,Flash和EPROM。TMS320C6713与外部I/O接口通过FFA构造的I/O端口、HPI口、多缓冲串口(McBSP)、SPI口等几种方式实现。与专用的硬件压缩器件相比,TMS320C6713B可方便实现数据压缩。以及系统升级和配置灵活。

评论