DDR存储器电气特性验证

前言

几乎每一个电子设备,从智能手机到服务器,都使用了某种形式的RAM存储器。尽管闪存NAND继续流行(由于各式各样的消费电子产品的流行),由于SDRAM为相对较低的每比特成本提供了速度和存储很好的结合,SDRAM仍然是大多数计算机以及基于计算机产品的主流存储器技术。DDR是双数据速率的SDRAM内存,已经成为今天存储器技术的选择。DDR技术不断发展,不断提高速度和容量,同时降低成本,减小功率和存储设备的物理尺寸。

随着时钟速率和数据传输速率不断增加和性能的提高,设计工程师必须保证系统的性能指标,或确保系统内部存储器和存储器控制设备的互操作性,存储器子系统的模拟信号完整性已成为设计工程师越来越多重点考虑的问题。许多性能问题,甚至在协议层发现的问题,也可以追溯到信号完整性问题上。因此,存储器的模拟信号完整性验证已经成为很多电子设计验证关键的一步。

JEDEC(电子工程设计发展联合协会)已经明确规定存储设备详细测试要求,需要对抖动、定时和电气信号质量进行验证。测试参数:如时钟抖动、建立和保持时间、信号的过冲、信号的下冲、过渡电压等列入了JEDEC为存储器技术制定的测试规范。但执行规范里的这些测试是一个很大的挑战,因为进行这些测试很可能是一个复杂而又耗时的任务。拥有正确的工具和技术,可以减少测试时间,并确保最准确的测试结果。在本应用文章中,我们将讨论针对存储器测试的解决方案,这个方案能够帮助工程师战胜挑战和简化验证过程。

信号的获取和探测

存储器验证的第一个难点问题是如何探测并采集必要的信号。JEDEC标准规定的测试应在存储器元件的BGA(球栅阵列结构的PCB)上。而FBGA封装组件包括一个焊球连接阵列(这是出于实际目的),无法进入连接,如何进行存储器的探测呢?

一种解决方案是在PCB布线过程中设计测试点,或探测存储器元件板的背面的过孔。虽然这些测试点没有严格在“存储器元件附近”,PCB走线长度一般都比较短,对信号衰减的影响很小。当使用这种方法探测时,信号完整性通常是相当不错的,可以进行电气特性的验证。

图1 DDR3双列直插内存模块(DIMM)“背面”的测试点

对于这种类型应用,可以使用手持探头,但是在多个探头前端和测试点同时保持良好的电接触非常困难。

考虑到有些JEDEC的测量要求三个或更多的测试点,加上其他信号如芯片选择信号、RAS和CAS可能需要确定存储器状态,许多工程师常常选择使用焊接式探头进行连接。

泰克公司开发了一种专为这种类型的应用设计的探测解决方案。P7500系列探头有4~20GHz的带宽,是存储器验证应用的选择。图2说明了几个可用的P7500系列探头前端之一,这种探头非常适合存储器验证的应用。这些微波同轴”前端在需要多个探测前端进行焊接情况时提供了有效的解决方案,同时提供优秀的信号保真度和4GHz带宽,足已满足存储器DDR3@1600MT/s的测试需求。

图2 P7500系列微波同轴探头焊接到DIMM上

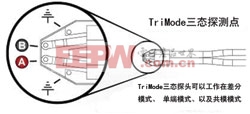

P7500系列探头针对存储器测试应用的另一个优点是泰克专有的TriMode(三态)功能。这种独特的功能允许探头不但可以测试+和-差分信号,又可以测试单端信号。使用探头前端的三个焊接连接,用户就可以使用探头上控制按钮或在示波器菜单来对差分和单端探测模式之间进行切换。使用焊接探头的+连接到单端数据或地址线,使用焊接探头的-连接到另一相邻线。然后用户可以使用一个探头,通过两个单端测量模式之间切换,很容易地测量其中任何两个信号。

图3 P7500三态前端连接

然而,很多情况下通过背面过孔探测信号可能不是一种好的选择。使用嵌入式存储器设计,存储器元件背面可能没有可用的板上空间。甚至很多标准的DIMM,在板的两面都有存储器元件,以增加存储密度。这种情况下,测试工程师怎样才能探测到测试点呢?

幸运的是,即使这样情况,现在也有探测解决方案。泰克公司与Nexus科技公司合作开发了所有标准DDR3和DDR2存储器设备转接板内插板组件。这些转接板内插板使用插槽代替存储器元件连接到被测设备。在转接板有探测的测试点,然后对齐到插槽上的位置。存储器元件再插到转接板上。图4是这种“连接”的示意图。

图4 DDR转接板内插板组件

评论