3D封装材料技术

未来封装用的先进材料

3D安装用的新型衬底一般为超薄多层板。此材料的主要特点是:优良的静态弯曲能力;高抗热性;多层工艺时极好的尺寸稳定性。采用这些材料可以为3D安装PWB实现又薄又能弯曲的多层板。

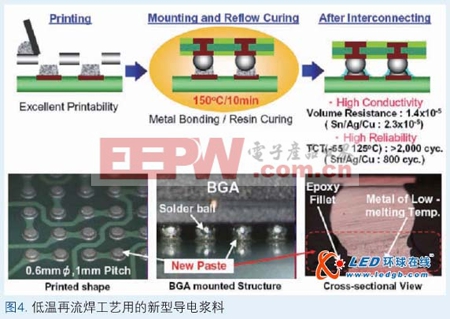

开发了适用于低温再流焊工艺的新型导电浆料。这种新颖浆料是由低熔点金属和高抗热性热固树脂系组成。它形成金属键合和树脂带,能增强150℃再流焊工艺后的互连(图4)。金属键合减少了连接电阻,树脂带提高了TCT中连接的可靠性。采用此浆料可以方便地降低再流焊温度,以减少超薄封装的翘曲。

结论

SiP、3D封装将广泛用于各个电子学领域。新型材料包括了多芯片叠层封装用的芯片键合膜、PoP用的衬底和环氧模塑料、先进倒装芯片封装用的底充胶材料、3D安装用的新型衬底和低温再流焊工艺用的新型导电胶等。对3D封装材料的研究和探讨将提高3D封装性能并降低成本。

3D封装

当追随摩尔定律成为产业共识,More Moore的提出似乎又为芯片制造业的发展增添了些许亮色。一般来说,More Moore指芯片特征尺寸的不断缩小,它包括两方面:为提高密度、性能和可靠性在晶圆水平和垂直方向上继续缩小特征尺寸;采用3D结构等工艺技术以及新材料的运用来影响晶圆的电学性能。

随着消费电子设计降低到45nm甚至更小节点,为了在芯片内塞进更多功能,3D封装应运而生。手机是加速开发3D封装的主动力。手机已从低端向高端发展,要求体积小,重量轻且功能多。为此,高端手机用芯片必须具有强大的内存容量,于是诞生了芯片堆叠的封装(SDP),如多芯片封装(MCP)和堆叠芯片尺寸封装(SCSP)等;另外,在2D封装中需要大量长程互连,导致电路RC延迟的增加。为了提高信号传输速度,必须降低RC延迟。可用3D封装的短程垂直互连来替代2D封装的长程互连。

3D封装技术优势众多:

在尺寸和重量方面,3D设计替代单芯片封装缩小了器件尺寸、减轻了重量。与传统封装相比,使用3D技术可缩短尺寸、减轻重量达40-50倍;

在速度方面,3D技术节约的功率可使3D元件以每秒更快的转换速度运转而不增加能耗,寄生性电容和电感得以降低;

3D封装更有效的利用了硅片的有效区域,与2D封装技术相比,3D技术的硅片效率超过100%;

在芯片中,噪声幅度和频率主要受封装和互连的限制,3D技术在降低噪声中起着缩短互连长度的作用,因而也降低了互连伴随的寄生性。

电路密度的提高意味着提高功率密度。采用3D技术制造元器件可提高功率密度,但必须考虑热处理问题。一般需要在两个层次进行热处理,第一是系统设计,即将热能均匀的分布在3D元器件表面;第二是采用诸如金刚石低热阻基板,或采用强制冷风、冷却液来降低3D元器件的温度。为了持续提高电路密度、性能和降低成本,芯片尺寸不断缩小,意味着设计复杂度的提高。然而,3D技术目前只完成了少量复杂的系统及元器件,因此还要改进设计以解决系统复杂度不断增加的问题。

任何一种新技术的出现,其使用都存在着预期高成本的问题,3D技术也不例外。影响叠层成本的因素有:叠层高度及复杂性;每层的加工步骤数目;叠层前在每块芯片上采用的测试方法;硅片后处理等等。

3D封装改善了芯片的许多性能,如尺寸、重量、速度、产量及耗能。当前,3D封装的发展有质量、电特性、机械性能、热特性、封装成本、生产时间等的限制,并且在许多情况下,这些因素是相互关联的。3D封装开发如何完成、什么时候完成?大多数IC专家认为可能会经历以下几个阶段。具有TSV和导电浆料的快闪存储器晶圆叠层很可能会发展,随后会有表面凸点间距小至5μm的IC表面-表面键合出现。最后,硅上系统将会发展到存储器、图形和其它IC将与微处理器芯片相键合。

评论