集成的半导体光电智能探测器SOC研究

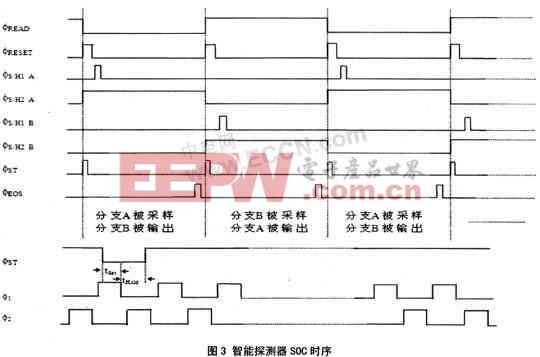

在实践上,我们根据图2、图3所示的原理,使用开关电容技术实现了低噪声、高读出速度的智能探测器电路设计。由于篇幅所限,具体电路结构本文不再赘述。具体的测试结果见本文第5部分。

4 工艺设计

本电路采用1μm准双阱硅栅CMOS工艺制造,探测器部分基本结构如图4所示。我们力求在标准CMOS工艺的基础上做少量修改,保证在不影响正常工艺步骤的情况下,加入少量几个工艺步骤,在同一芯片上,制备出高性能光电二极管。与常规CMOS工艺相比,主要有如下特殊之处:

(1)P阱版

在电路区,与常规的P阱版没有差异。对光电二极管,本次P阱注入形成保护环和接触区。

(2)N阱版

在标准CMOS工艺中,不必进行这次光刻,只要对整个硅片进行大面积注入即可。但是,对于智能探测器工艺,由于存在光电二极管区,因此不能进行这样处理。我们在P阱注入后再加入一块N阱版,挡住光电二极管区,只对电路区进行注入,这样,就达到了分别优化的目的。

(3)P阱场注和有源区注入

这次光刻是利用常规CMOS工艺的P阱场注形成光电二极管的有源区注入,该步骤有待于优化。

(4)P+注入

如图4所示,本次注入在形成电路的P+区的同时,还对光电二极管的接触区进行了P+注入,以形成良好的接触。

(5)孔版

常规CMOS工艺一次即可刻出接触孔,但对光电二极管,不但要刻接触孔,而且还要刻掉光电二极管光敏面上的LPCVD层,因此,如3.1节所述,我们使用“孔版”和“孔和有源区版”来达到此目的。第一次光刻接触孔和光电二极管的有源区,腐蚀掉LPCVD层,第二次光刻所有的接触孔,腐蚀掉氮化硅层和二氧化硅层。

评论