基于USB2_0和DDR2的数据采集系统设计与FPGA实现

2.2 IF模块设计

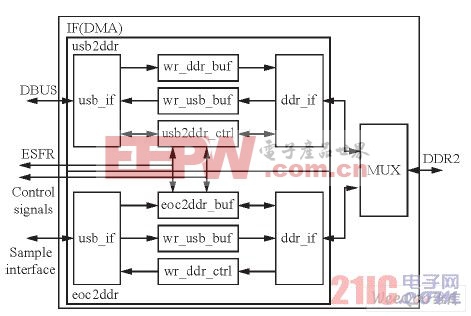

IF模块负责接口的转换和数据传输的控制,其结构如图2所示。其中, usb2ddr和eoc2ddr子模块分别控制USB2.0与DDR2 SDRAM、外部采集接口与DDR2 SDRAM之间数据的上下行传输。

上下行数据传输分别由usb2ddr_ctrl 和eoc2ddr_ctrl模块中的状态机进行控制和管理。其中采集模式和深度由MCU的ESFR总线配置, 而传输开始信号则使用MCU的PORT0 [0]、PORT0[1], 结束信号连接在MCU的外部中断NINT0和NINT1上, 这样可使MCU能够及时响应。上行采集开始后, 首先使eoc2ddr_ctrl中的控制状态机处于写状态, 并不断地比较DDR2的地址与配置深度, 直到采集完成。然后再使usb2ddr_ctrl中的控制状态机处于读状态, 同样也比较地址与深度,直到数据读取完成。下行传输过程则与之相反。

IF模块结构框图

图2 IF模块结构框图。

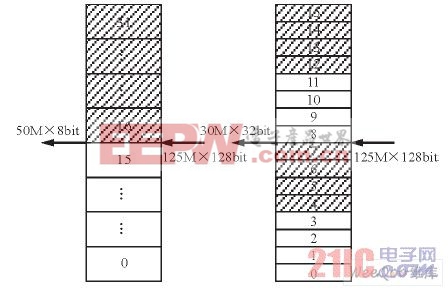

由于各个接口上数据传输的速率不同, 因此, 数据传输时, 要异步FIFO或者缓存。在本设计中, 由于各接口速率固定, 因此, 可采用双端口RAM作乒乓缓存方式以提高效率并保证数据连续, 图3所示是乒乓缓存原理图。

乒乓缓存原理图

图3 乒乓缓存原理图。

当下行发出数据时, 从DDR2的125 M×128bit到50 M×8 bit所需要的最小深度为32×8 bit, 因为从SDRAM中读数据的最大延迟是26个DDR2时钟周期(即208 ns), 而将DDR2读出的128 bit发出则需要16个时钟周期(即320 ns), 因此, 为了保证发出的数据可连续进行乒乓操作, 需要2×128bit的深度。同理, 在上行数据从DDR2的125 M×128 bit到USB的30 M×32 bit则需要4×128 bit深度,因为USB时钟读完128 bit数据需要133.2 ns, 小于SDRAM 读数据延迟的208 ns, 因此, 每次从SDRAM中读2×128 bit数据时, 其乒乓操作就至少需要4×128 bit深度。

3 系统的改进

本数据采集系统对传统的数据采集系统做了创新型改进。改进主要是三个方面: 一是对数据采集的深度实行可配置模式; 二是在功能上不仅作为数据采集系统, 还能作为数据发生器, 即将采集到计算机上的数据通过数据采集系统发送出来; 三是该数据采集系统有两种工作模式, 即普通采集模式和触发采集模式。

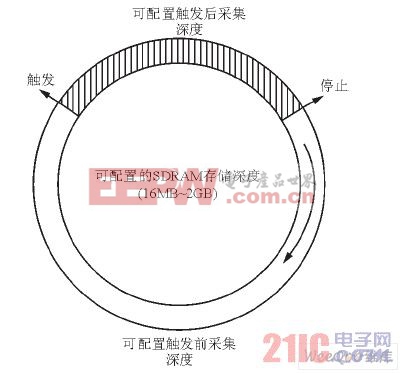

深度可配置增加了系统在使用过程中的灵活性。该系统除了采集数据外, 还能将数据发出来用于芯片的FPGA原型验证, 从而避免了缓慢的大数据量仿真, 更增强了系统的实用性。通过ESFR配置8 bit的深度寄存器可实现以16 MByte为单位的深度调节。触发是数据采集系统不可缺少的功能, 因此, 该数据采集系统分为普通采集模式和触发采集模式。触发采集模式的原理如图4所示。在触发模式中, 可将SDRAM看做一个圆形的循环存储器, 触发前后的采集深度同样也可以通过ESFR配置, 从而实现触发前后的采集深度比例可调。

触发实现机制原理图

图4 触发实现机制原理图。

评论