DDR SDRAM在高速数据采集系统中的应用

|

机的动作,通过翻译控制信号控制内部状态机产生控制DDR的正确时序信号,这一部分是主控制模块的关键和难点,能否正确控制DDR的操作完全集中在此模块

(2)外部刷新模块是辅助主状态机模块控制DDR处于空闲状态时的定时刷新

(3)地址发生模块的作用是根据所接收由主控状态机发送来的内部命令产生所对应的地址,然后将命令和对应的地址同步发送给命令发送模块

(4)命令发生模块是与DDR芯片的接口部分,其将从地址模块发送来的具体命令解释成DDR所需的命令信号和控制信号![]()

以及所需的地址信号

以及所需的地址信号![]() (AO~A12,BA0,BAl)

(AO~A12,BA0,BAl)

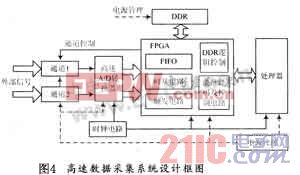

为了能更清楚地了解DDR在高速数据采集系统中的应用,这里将对基于CPCI总线的高速数据采集系统结构进行描述 高速数据采集系统的设计框图如图3所示

高速数据采集系统的设计框图如图3所示

|

外部信号首先经过模拟通道的调理达到A/D芯片的输入要求,再通过A/D芯片将模拟信号转换成数字信号送人FPGA处理 当处理器发出写命令时,把数字信号在FIFO内部进行缓存再送入DDR进行存储.如果A/D的采样速率为200 MSa/s,则可以使用133 MHz时钟速率的DDR芯片即可达到要求

当处理器发出写命令时,把数字信号在FIFO内部进行缓存再送入DDR进行存储.如果A/D的采样速率为200 MSa/s,则可以使用133 MHz时钟速率的DDR芯片即可达到要求 但是在内部进行缓存时存在一个问题,就是写入F1F()的时钟速率大于读取FIFO的时钟速率,这样就会导致从A/D采样过来的信号不能完整地存储

但是在内部进行缓存时存在一个问题,就是写入F1F()的时钟速率大于读取FIFO的时钟速率,这样就会导致从A/D采样过来的信号不能完整地存储

在这种情况下通常采用数据分流的方式进行解决,即把采人FPGA的200 MHz的数据流分成2路100 M的数据流,分别存入相应的FIFO内再以133 MHz的时钟速率读出送DDR进行存储,这样就可以对信号进行完整的存储 当然存储过程还要通过DDR的控制模块和FPGA内部自带的1P核的配合才能够完成

当然存储过程还要通过DDR的控制模块和FPGA内部自带的1P核的配合才能够完成 同理,当处理器发出渎命令时,在DDR控制模块的控制下将DDR内部数据读回FPGA内部,再次通过FIFO进行缓存

同理,当处理器发出渎命令时,在DDR控制模块的控制下将DDR内部数据读回FPGA内部,再次通过FIFO进行缓存 通常采用40 M的时钟速率将数据送回处理器处理,从DDR写回FPGA的数据流时钟速率为133 M,而从FIFO读}IJ数据的时钟速率为40 M;同样存在着写入FIFO的时钟速率大于读取的时钟速率的现象,但足这里不仔在数据丢火的问题,冈为前端的分流处理已经保证了数据的完整性

通常采用40 M的时钟速率将数据送回处理器处理,从DDR写回FPGA的数据流时钟速率为133 M,而从FIFO读}IJ数据的时钟速率为40 M;同样存在着写入FIFO的时钟速率大于读取的时钟速率的现象,但足这里不仔在数据丢火的问题,冈为前端的分流处理已经保证了数据的完整性 这里只需对FIFO及DDR进行控制,即对FIFO的使用率做一个控制,当FIFO的使用率大于某一值时,停止从DDR中读取数据;当小于这个值时,继续从DDR中读取数据

这里只需对FIFO及DDR进行控制,即对FIFO的使用率做一个控制,当FIFO的使用率大于某一值时,停止从DDR中读取数据;当小于这个值时,继续从DDR中读取数据 这样就有足够的数据可进行分析处理,从而重现信号特征

这样就有足够的数据可进行分析处理,从而重现信号特征

5 结 语

DDR在高速数据采集系统中的应用有很大的实际意义,他提高了系统的可靠性和数据的存储深度,在一定程度上有效地减小了电路设计的尺寸 DDR已经被应用于视频采集、内存设计等多个领域

DDR已经被应用于视频采集、内存设计等多个领域 其关键技术是DDR时序控制模块的设计

其关键技术是DDR时序控制模块的设计

评论