基于架构与基于流程的DFT测试方法之比较

ASIC设计的平均门数不断增加,这迫使设计团队将20%到50%的开发工作花费在与测试相关的问题上,以达到良好的测试覆盖率。尽管遵循可测试设计(DFT)规则被认为是好做法,但对嵌入式RAM、多时钟域、复位线和嵌入式IP的测试处理将显著影响设计进度。即使解决了上述所有问题,开发者也几乎不可能达到100%的粘着性故障(stuck-at fault)覆盖率。其结果是,ASIC设计常常在故障覆盖率低于90%的情况下就投入生产,从而造成不必要的器件缺陷率和板级故障。

本文引用地址:http://www.eepw.com.cn/article/194923.htm基于流程的方法

为了在一个设计中插入扫描测试结构,第一个要做的步骤是用扫描触发器替换所有的触发器。有时候,这可以当成综合过程的一部分来做,尽管它以往是在设计流程的后期完成。插入扫描触发器允许更高程度地控制设计中的各个节点,从而提高故障覆盖率。不过,传统的扫描技术不能完全控制或观测设计中的所有用户网络,因而会留下许多未测试的结构。

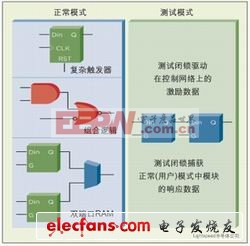

最常见一类的扫描触发器在数据输入端的前面包含一个多路复用器。在测试模式中,这使得数据可以被移进触发器;在用户模式中,这允许一个正常的逻辑信号被存储。

传统的ASIC扫描测试通常需要以下步骤:

1、准备一个测试时钟,而且测试电路必须允许该时钟施加到所有扫描触发器上。

2、在测试期间,所有触发器均处于测试模式。

3、在用户模式操作期间,所有触发器均处于正常工作模式。

值得注意的是,当采用基于多工器的扫描触发器时,多路复用器通常被插在用户时钟的主路径上,以便在测试模式下测试时钟可以被传递给所有触发器。所有触发器将同时被设置为测试模式。

为达到足够的故障覆盖率和可接受的器件缺陷率,传统的测试技术需要许多DFT规则。不遵循DFT规则的后果是,许多故障无法采用传统扫描方法进行测试,从而使总的故障覆盖率受损。

为了获得合理的粘着性故障覆盖率,一个设计通常必须是全同步的。因此,这成为第一个DFT规则。不幸的是,许多设计、特别是网络和通信领域的设计需要多个异步时钟,这就不可能不违反这条规则。而且,为了追求速度,综合过程经常会产生重收敛的冗余逻辑结构,这又是违反规则的。

公认的DFT规则包括:

1、设计必须以一个公共时钟为准,保持完全同步。

2、在测试期间,存储单元的异步输入必须由一个外部引脚去使能。

3、只能使用专为支持自动测试模式生成(ATPG)而设计的连续库单元。有时要禁止使用下降沿触发的触发器。

4、不允许有门控时钟。它们在测试期间必须旁路掉。

5、不应使用内部三态总线;首选是多路复用器。

6、不允许有组合逻辑环路;不允许有重收敛的冗余逻辑。

7、在测试期间,外部总线必须禁止使能。

8、包含不同测试方法的各个IP模块之间的接口必须是完全可测试的。

自动测试

实现自动测试的前提是:如果所有与测试相关的电路都嵌入在基础阵列中,那么与测试相关的事情就可以从ASIC开发过程中去除。嵌入的自动测试电路不仅独立于用户设计,而且是在获知用户设计之前构建的。

因为自动测试电路嵌入在ASIC的基础结构中,所以它的工作方式与传统的扫描测试非常不同。

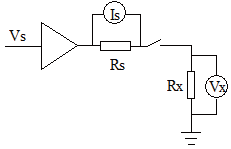

用于传统ASIC的扫描测试方法要求设计中的所有扫描触发器在同一时间内处于测试模式,而自动测试的顺序操作方式允许在任何特定的测试周期内,一些模块处于测试模式,而其它模块仍处于正常模式。在自动测试ASIC内的功能模块具有“控制”和“观测”能力。

通过隔离单独的模块和网络,这使得开发者可以对制造过程进行测试,以完全验证硅片的完整性,而无需考虑用户设计和DFT规则。

为达到这个目的,开发者还需要一种新类型的模块。这种模块内独特的Q_Cell包含“控制”和“观测”能力,并且能够被配置成组合逻辑、触发器或RAM。这意味着所有网络都能够被控制,而不论它们是代表时钟还是置位/复位,也不论它们是否是冗余结构或组合逻辑环路的一部分。

一种四输入多工型单元(P_Cell)可以用来实现大多数组合功能,或者与Q_Cell组合在一起,以实现像全加器这样的复杂功能。

自动测试不仅能同时捕获器件内所有信号的状态,而且还能恢复那些状态,因此操作可以从任何指定的初始条件下开始。存储器和触发器可以被预置,以仿真故障或异常的功耗偏差。这个功能对于现场诊断问题很有用。

自动测试是一种软硬件结合的测试方法,它取消了所有的DFT规则,并且总能提供100%的粘着性故障覆盖率。随着质量要求和器件复杂度的增高,这种覆盖率变得越来越重要。自动测试已经成功地用于100多个结构化ASIC设计中,但它也可以应用于标准单元ASIC设计。

评论