高速模数转换器动态参数的测试

高速模数转换器(ADC)的参数定义和描述如表1所示。

本文引用地址:http://www.eepw.com.cn/article/194384.htm表1 动态参数定义

测试方案中的线路板布局和硬件需求

为合理测试高速ADC的动态参数,最好选用制造商预先装配好的电路板,或是参考数据手册中推荐的线路板布局布板,高速数据转换器的布板需要高速电路的设计技巧,通常应遵守以下基本规则:

所有的旁路电容尽可能靠近器件安装,最好和ADC在同一层面,采用表面贴装元件使引线最短,减小寄生电感和电容。

模拟电源、数字电源、基准电源和输入公共端采用两个0.1MF的陶瓷电容和一个2.2M(F双极性电容并联对地旁路。

采用具有独立的地平面和电源平面的多层电路板,保证信号的完整性。

采用独立的接地平面时应考虑ADC模拟地和数字地的物理位置。两个地平面之间的阻抗要尽可能低,二者间的交流和直流电压差低于0.3V以避免器件的损坏和死锁。模拟地与数字地应单点连接,可以用低阻值表贴电阻(1Ω~5Ω)、铁氧体磁珠连接或直接短路,避免充满噪声的数字地电流对模拟地的干扰。

如果模拟地与数字地充分隔离时,也可以将所有的接地引脚置于同一平面。

高速数字信号线应远离敏感的模拟信号线。

所有的信号线应尽可能短,而且无90(拐角。

时钟输入要作为模拟输入信号来处理,远离任何模拟输入和数字信号。

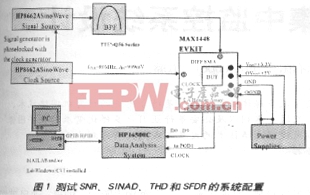

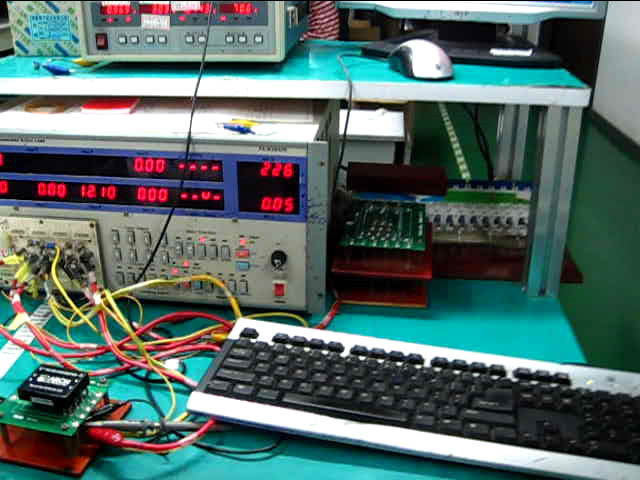

选择恰当的测试方案和正确的测试设备是获得数据转换器最佳参数的重要环节。以下提出的硬件选择方案对高速ADC MAX1448的测试是必需的,也是行之有效的。

直流电源 (Hewlett Packard E3620A, 双电源 0-25V, 0-1A): 为模拟和数字电路提供独立的供电电源。每个电源必须能够提供100mA 的驱动电流.

时钟信号函数发生器 (Hewlett-Packard HP8662A): 被测器件的时钟输入端接受兼容于CMOS电平的时钟信号。由于MAX1448内部采用十级流水线结构、级间转换依赖于外部时钟上升沿和下降沿的可重复性,所以需用一个低抖动、快速上升/下降的外部时钟信号。尤其是本转换器的采样出现在时钟信号的下降沿,应确保下降沿的抖动最小。孔径抖动限制了ADC的SNR性能:

SNRdB = 20·log10 (1 / 2π·fIN·TAj)

式中fIN 为模拟输入频率,tAJ 为孔径抖动时间。欠采样应用中对时钟抖动指标要求更严格。

输入信号函数发生器 (Hewlett-Packard HP8662A):

为保证正常工作,两个函数发生器(时钟与输入信号)必须是相位锁定的。

逻辑分析仪- (Hewlett-Packard HP16500C):

根据FFT所需的采样点选择逻辑分析仪,如HP1663C具有不到4k的数据记录容量,可以用于本测试中。

模拟带通滤波器(TTE 椭圆函数带通滤波器 Q56 系列):

截止频率:7.5MHz, 20MHz, 40MHz 和 50MHz

数字万用表 (DMM): 用于检查基准、电源和共模电压。

被测器件的评估板

采用源自电路板的外部时钟信号同步逻辑分析仪,并在时钟的上升沿锁相。采集数据时,数据可以存储在数据采集板上、通过逻辑分析仪的HPIB总线进行数据交换,也可以存储在逻辑分析仪的硬盘或软盘中。

接着要考虑的是选择合适的软件工具。下列软件工具被选择用于数据的采集和分析:

* LabWindows/CVI:在逻辑分析仪和数据采集板之间建立通讯链路并进行数据采集。

* MATLAB:用于对所采集的数据进行FFT和动态参数分析的软件工具,源程序可由Maxim中文网站获得(www.maxim-ic.com.cn)。

用于测试的总体电路框图如图一所示。

评论