浅谈FPGA设计原则与技巧

前言

本文引用地址:http://www.eepw.com.cn/article/193067.htmFPGA(Field-Programmable Gate Array),即现场可编程门阵列,作为专用集成电路领域中的一种半定制电路,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展下的产物。近几年来由于FPGA器件的应用十分广泛,而FPGA设计是使用FPGA器件必不可少的一部分,所以了解与掌握有关FPGA设计知识是十分必要的。

FPGA设计的基本原则及常用模块

基本原则:一 面积和速度的平衡与互换;二硬件原则;三 系统原则;四 同步设计原则;

常用模块:一 RAM;二 FIFO;三 全局时钟资源与时钟锁相环;四 全局复位、置位信号

四种常用FPGA设计思想与技巧

FPGA设计思想与技巧是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA设计工作种取得事半功倍的效果。常用的FPGA设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步方法。

FPGA设计思想之一乒乓操作

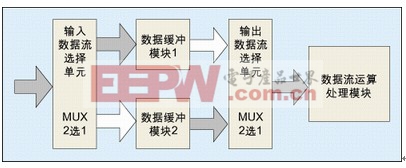

“乒乓操作”是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如图1所示。

乒乓操作的处理流程为:输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM)、单口RAM(SPRAM)、FIFO等。在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”;在第2个缓冲周期,通过“输入数据选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1个周期数据通过“输入数据选择单元”的选择,送到“数据流运算处理模块”进行运算处理;在第3个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,同时将“数据缓冲模块2”缓存的第2个周期的数据通过“输入数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。如此循环。

图2:采用双口RAM,并在DPRAM后引入一级数据预处理模块实现用低速模块处理高速数据流。

另外,巧妙运用乒乓操作还可以达到用低速模块处理高速数据流的效果。如图2所示,数据缓冲模块采用了双口RAM,并在DPRAM后引入了一级数据预处理模块,这个数据预处理可以根据需要的各种数据运算,比如在WCDMA设计中,对输入数据流的解扩、解扰、去旋转等。假设端口A的输入数据流的速率为100Mbps,乒乓操作的缓冲周期是10ms。

通过乒乓操作实现低速模块处理高速数据的实质是:通过DPRAM这种缓存单元实现了数据流的串并转换,并行用“数据预处理模块1”和“数据预处理模块2”处理分流的数据,是面积与速度互换原则的体现!

串并转换设计技巧

串并转换是FPGA设计的一个重要技巧,它是数据流处理的常用手段,也是面积与速度互换思想的直接体现。FPGA设计思想中的串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、RAM等实现。前面在乒乓操作的图例中,就是通过DPRAM实现了数据流的串并转换,而且由于使用了DPRAM,数据的缓冲区可以开得很大,对于数量比较小的设计可以采用寄存器完成串并转换。如无特殊需求,应该用同步时序设计完成串并之间的转换。比如数据从串行到并行,数据排列顺序是高位在前,可以用下面的编码实现:

prl_temp={prl_temp,srl_in};

其中,prl_temp是并行输出缓存寄存器,srl_in是串行数据输入。

对于排列顺序有规定的串并转换,可以用case语句判断实现。对于复杂的串并转换,还可以用状态机实现。

流水线操作设计思想

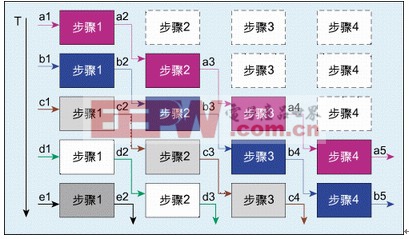

图3:流水线设计的结构示意图

流水线设计的一个关键在于整个设计时序的合理安排,要求每个操作步骤的划分合理。如果前级操作时间恰好等于后级的操作时间,设计最为简单,前级的输出直接汇入后级的输入即可;如果前级操作时间大于后级的操作时间,则需要对前级的输出数据适当缓存才能汇入到后级输入端;如果前级操作时间恰好小于后级的操作时间,则必须通过复制逻辑,将数据流分流,或者在前级对数据采用存储、后处理方式,否则会造成后级数据溢出。

在WCDMA设计中经常使用到流水线处理的方法,如RAKE接收机、搜索器、前导捕获等。流水线处理方式之所以频率较高,是因为复制了处理模块,它是面积换取速度思想的又一种具体体现。

图4:流水线设计时序示意图

数据接口的同步方法

数据接口的同步是FPGA设计的一个常见问题,也是一个重点和难点,很多设计不稳定都是源于数据接口的同步有问题。

在电路图设计阶段,一些工程师手工加入BUFT或者非门调整数据延迟,从而保证本级模块的时钟对上级模块数据的建立、保持时间要求。还有一些工程师为了有稳定的采样,生成了很多相差90度的时钟信号,时而用正沿打一下数据,时而用负沿打一下数据,用以调整数据的采样位置。这两种做法都十分不可取,因为一旦芯片更新换代或者移植到其它芯片组的芯片上,采样实现必须从新设计。而且,这两种做法造成电路实现的余量不够,一旦外界条件变换(比如温度升高),采样时序就有可能完全紊乱,造成电路瘫痪。

总结

由于FPGA既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,可以快速成品,也可以被修改来改正程序中的错误和更便宜的造价。所以电子工程师们开发设计是在普通的FPGA上完成然后将设计转移到一个类似于ASIC的芯片上。本文主要介绍了FPGA设计的基本原则和FPGA设计的思想与技巧。

评论