一种基于长码扩频技术的无人机遥控链路实现

摘要:为了满足无人机遥控链路远距离、高动态、强抗干扰能力的军事通信需求,设计了基于长码直接序列扩频技术的FPGA实现方案。该方案采用了一种基于FFT算法的快速伪码捕获方法,将传统的伪码相位与多普勒频移二维搜索过程简化为两者同时捕获的一维搜索过程。经过硬件实现与测试,该方案可有效减少硬件资源消耗,同时缩短捕获时间。

关键词:无人机遥控链路;直接序列扩频;长码捕获;FPGA

0 引言

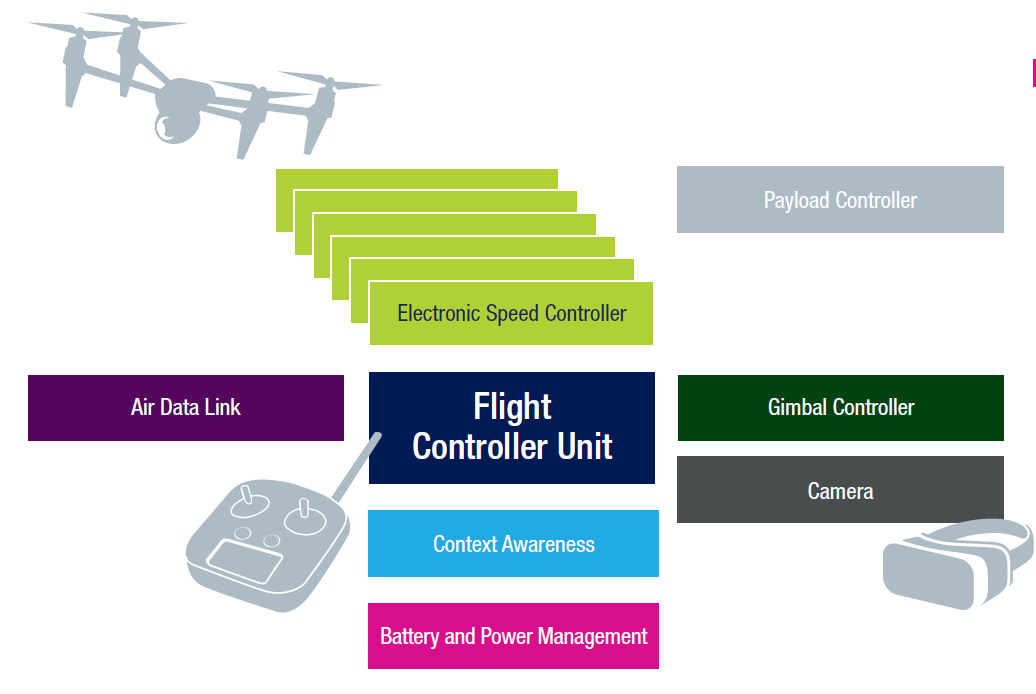

近年来,无人机在军事和民用领域得到了非常广泛的应用。无人机遥控链路是整个无人机系统的神经中枢,可靠性方面要求严格。无人机飞行时复杂多变的环境,特别是远距离巡航时,其低仰角带来的严重多径衰落与高速移动产生的多普勒效应严重影响其遥控链路的可靠性,为了提高其抗干扰能力,保证可靠性,通常采用直接序列扩频技术,并且要求较长的伪码长度。该技术的收发两端要求用完全相同的伪随机码进行扩频和解扩,因此接收机本地参考伪码序列与接收序列之间的精确同步是对接收信号实现解扩的关键,而伪码同步的关键是伪码捕获。

对于1 024位以上的长码扩频系统,传统的伪码捕获方法,捕获时间长,硬件资源消耗大,且动态性能低,不适应于无人机遥控链路。本文采用一种基于FFT算法的快速伪码捕获方法,设计了基于长码直接序列扩频技术的无人机遥控链路FPGA实现方案,经过硬件实现与测试,减少硬件资源消耗的同时缩短捕获时间。

1 遥控链路实现方案

该无人机遥控链路总体技术要求包括:信息速率为14.4 Kb/s;处理增益30 dB;扩频位数1 024位;码片速率22.5 Mb/s;纠错编码采用RS编码;多普勒频移不大于±20 kHz;同步时间小于10 ms;调制方式为QPSK。

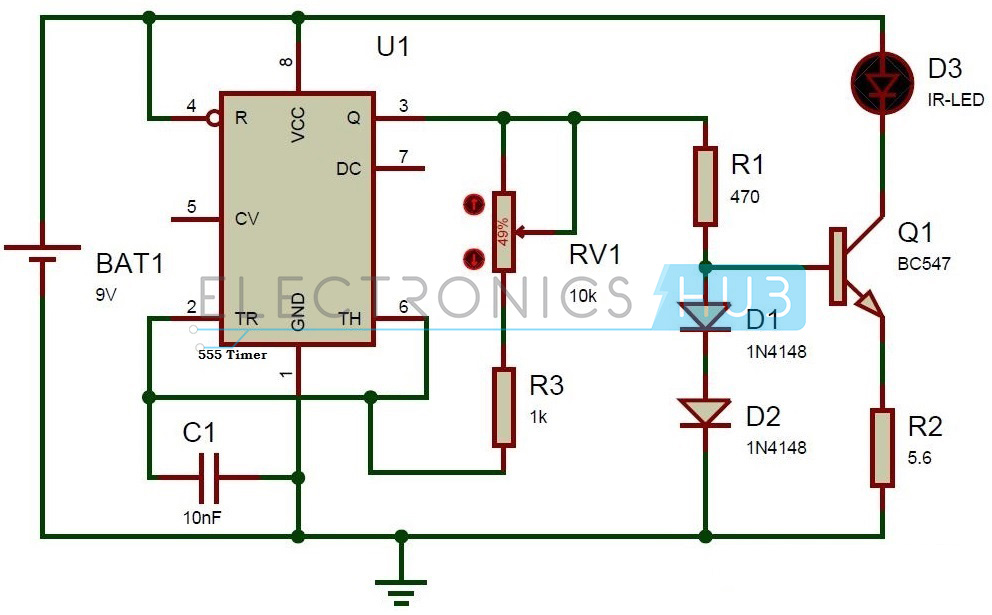

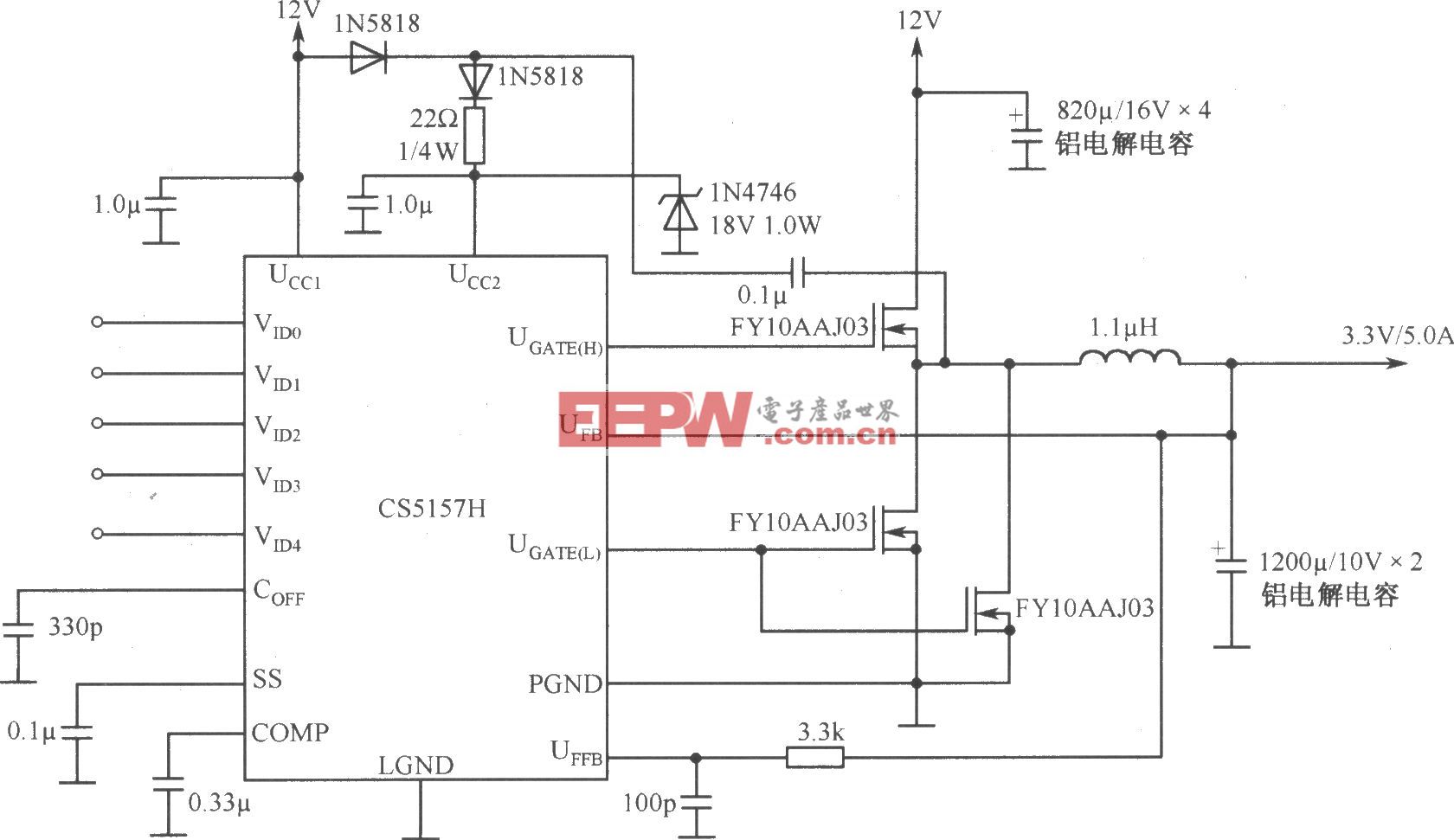

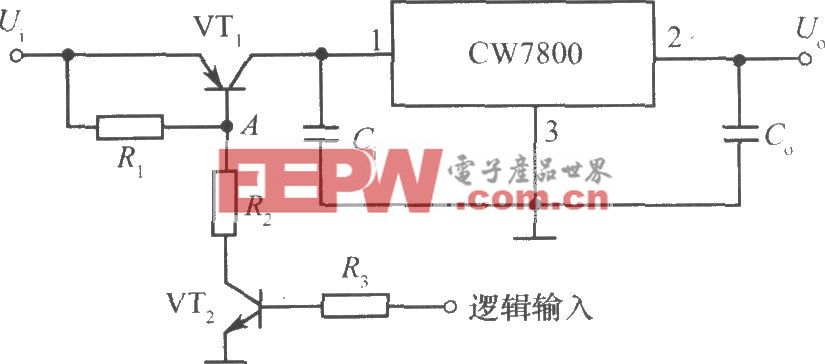

总体硬件实现方案如图1所示。采用收发一体的数字基带处理结构,收发通道在单片FPGA内完成。FPGA选用Altera公司的EP3C120F484,主要的功能都在片内完成,正交下变频解调器选用AD8348,它将中频140 MHz信号正交下变频到基带,形成I/Q两路正交信号,由ADC(AD92 16)完成基带信号的模-数转换,将形成的数字信号传输给FPGA。Si-4133产生中频本振,其工作频率为280 MHz,参考本振为10 MHz。主机接口芯片选用MAX3485,RS 422接口芯片,把解调后的信息传输给主机。其工作时钟频率为波特率的16倍。

1.1 发射通道实现方案

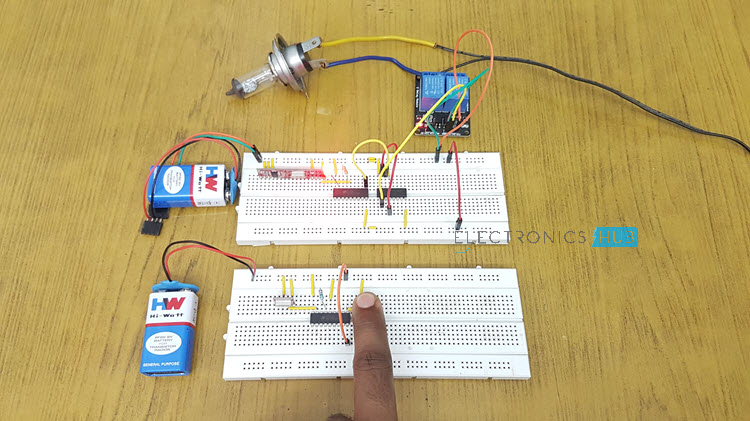

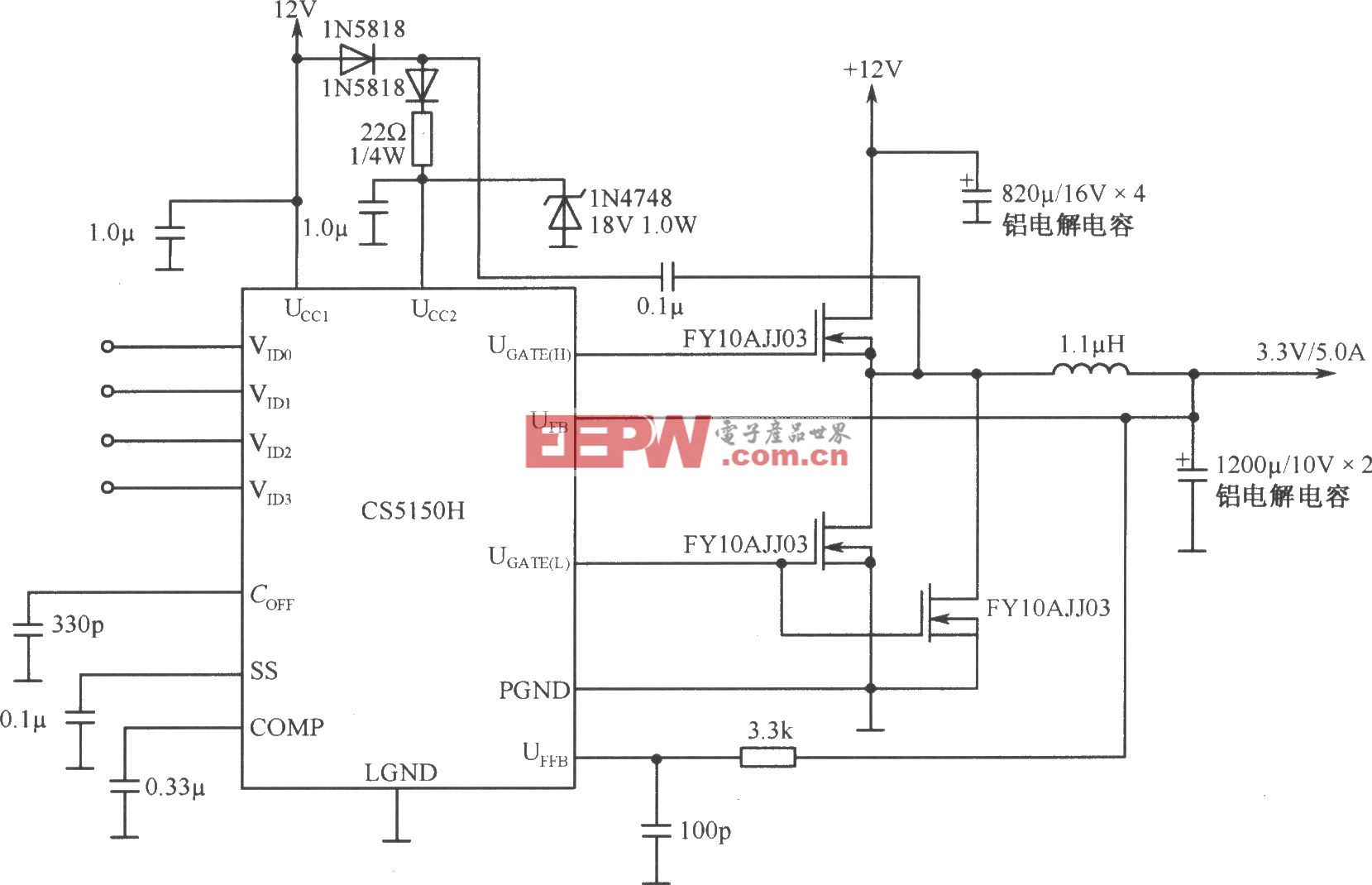

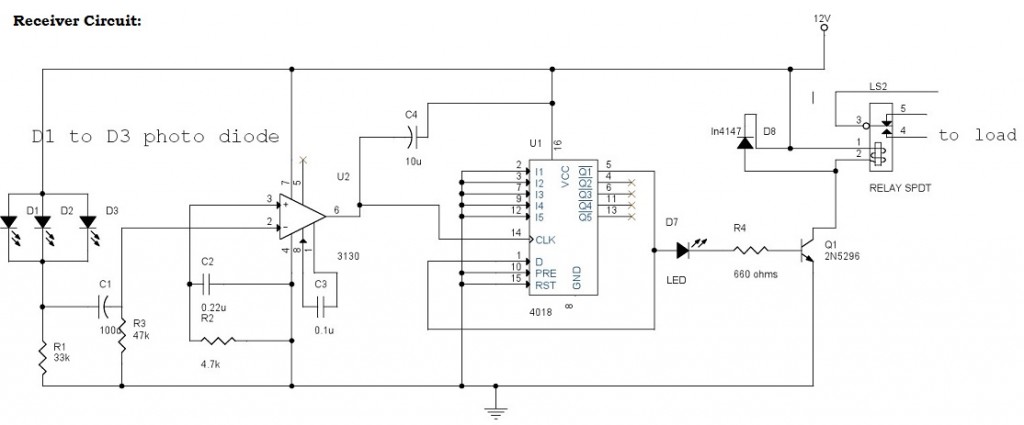

发射通道实现方案如图2所示。遥控指令数据经过RS编码,插入帧同步头,帧同步头采用13位巴克码,然后进行差分编码器,以消除相位模糊问题。随后,对产生的码元序列进行基带扩频,扩频码采用读PN码存储ROM方式产生。FPGA片内集成一个可调NCO,可对扩频后基带数据进行I,Q两路的平衡QPSK调制。调制器输出通过D/A变换送往射频单元。

评论