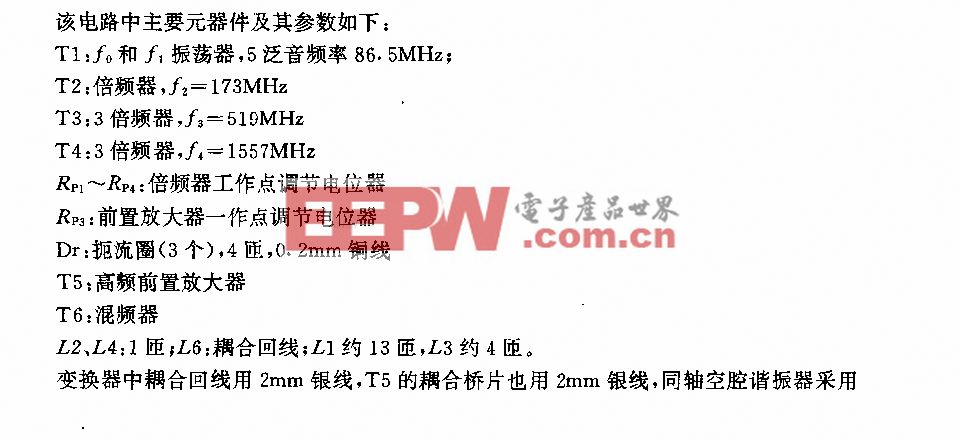

小型化数字测频接收机

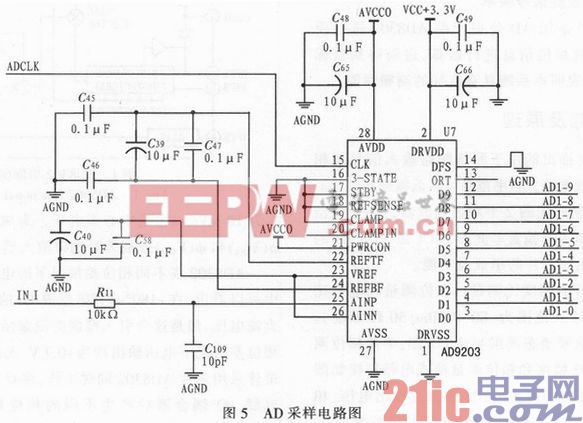

2.1 AD电路设计

由于目标信号可持续200 ns,因此选用采样率可达40MSPS的AD9203。AD9203为单端或差分输入,采样结果为10位并行输出,采用+3.3 V供电。AD9203采样电路如图5所示。在进行AD电路设计时,需要注意模拟供电与数字供电要分开,模拟地与数字地适当隔离,以减少数字电路对模拟电路的影响。本文引用地址:http://www.eepw.com.cn/article/192785.htm

2.2 控制电路设计

整个系统由FPGA控制,选用Xilinx公司产品Spartan3,该器件功能强大而且价格便宜。Spartan3主要完成发现被测信号,控制AD电路对鉴相器的输出电压进行采样,之后通过运算完成目标信号频率的测量,测量结果通过74HC245输出到下级电路。

2.3 软件编程

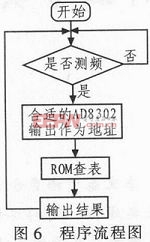

整个系统首先检测到目标信号的同步信号,控制AD电路进行采样,将电压采样结果作为查寻地址送到ROM查表得出频率。建立ROM查询表,用安捷伦公司的微波信号源产生1.4~2.0 GHz的标准信号,将AD8302的相位输出采样电压作为地址,与相应频率对应即可。由于AD8302在电压输出最大值与最小值附近线性性不是很理想,因此需要选择两路输出电压中合适的一路进行查表计算,并通过比较两路电压

以解模糊得到正确结果。最后将计算得出的频率输出到下级电路。整个程序的流程图如图6所示。

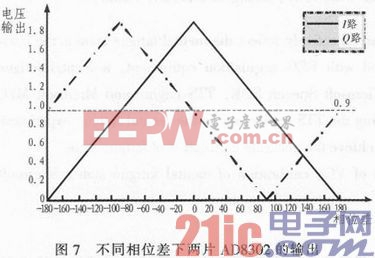

编程采用VHDL语言,主要部分是判断相位差属于-180°~0°还是0°~+180°,之后选取合适的一路输出电压作为地址进行寻址。举例来说,两片AD8302的输出如图7,比如+60°与60°的解模糊,从图中可见+60°时 I路大于0.9 V,Q路小于0.9 V;-60°时 I路、Q路均大于0.9 V,同时I路小于Q路。这样,可以根据I路、Q路和中间值0.9 V三者的关系来确定正确结果。

2.4 整体电路实现

由于本系统需要与其他部件组合使用,因此体积需要尽可能小。元器件全部采用缩小体积表面封装,并加装金属外壳以减少外界干扰。延迟线选用的同轴电缆长度相差285 cm,在输入信号频率变化时可得到理想的电压变化。图8所示为完整的测频接收机实物图。

3 测试结果

系统测试选用安捷伦公司的微波信号源,输出信号频率范围14~20 GHz,幅度为-20 dBmo经过测试,本系统测频范围为1.4~2.0GHz,测量精度达到10MHz,动态范围为-36~10dBm,性能良好。

4 结论

文中介绍了AD8302的典型应用,根据A08302的鉴相功能设计了IFM接收机,并制作了系统对电路进行验证。实验结果表明,根据AD8302设计的IFM接收机具有良好的测频功能,简化了系统设计。为了提高系统的性能,可以增加AD的有效位数,或者自己搭建比较器电路,经过改良,可以进一步提高测频精度和测频范围。

评论