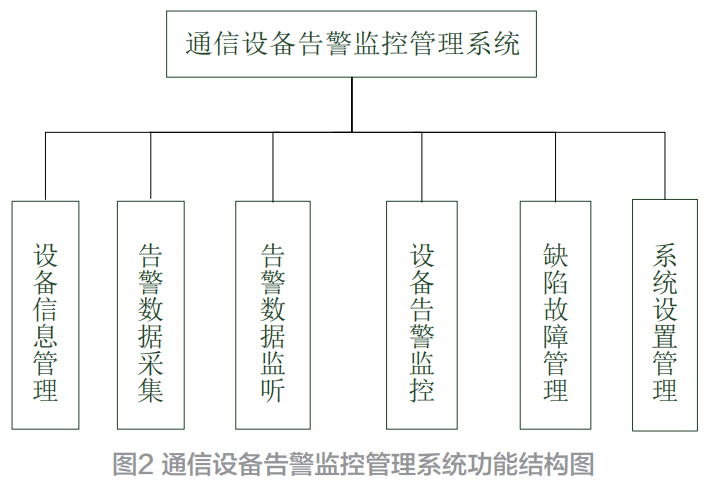

一种基于CPLD的数据采集控制板的设计

摘要:针对多种采集信号类型,设计了一种采用CPLD实现信号采集控制、信号处理、通讯及输出控制等功能的复合数据采集控制板,并分析了其相关应用性能。

关键词:CLPD EPP接口 编码器 数据采集

在需要采集多路模拟信号、开关信号、频率(计数)信号以及编码器信号等的数据采集应用中,利用通用板卡构成计算机测控系统是可行的,但对于产品的批量应用,其成本与综合性能不能令人满意。技术成熟的CPLD芯片的应用,可以很好地将逻辑控制、数据信号处理等功能集于一身,使以往需要利用多块信号板卡才能完成的任务整合于同一采集控制器中,从而有效地提高控制系统的可靠性,降低测控系统的实现成本。

本文设计一种基于CPLD的数据采集控制板。它能实现信号采集与控制、信号处理、通讯及输出控制等功能。

1 总体设计方案

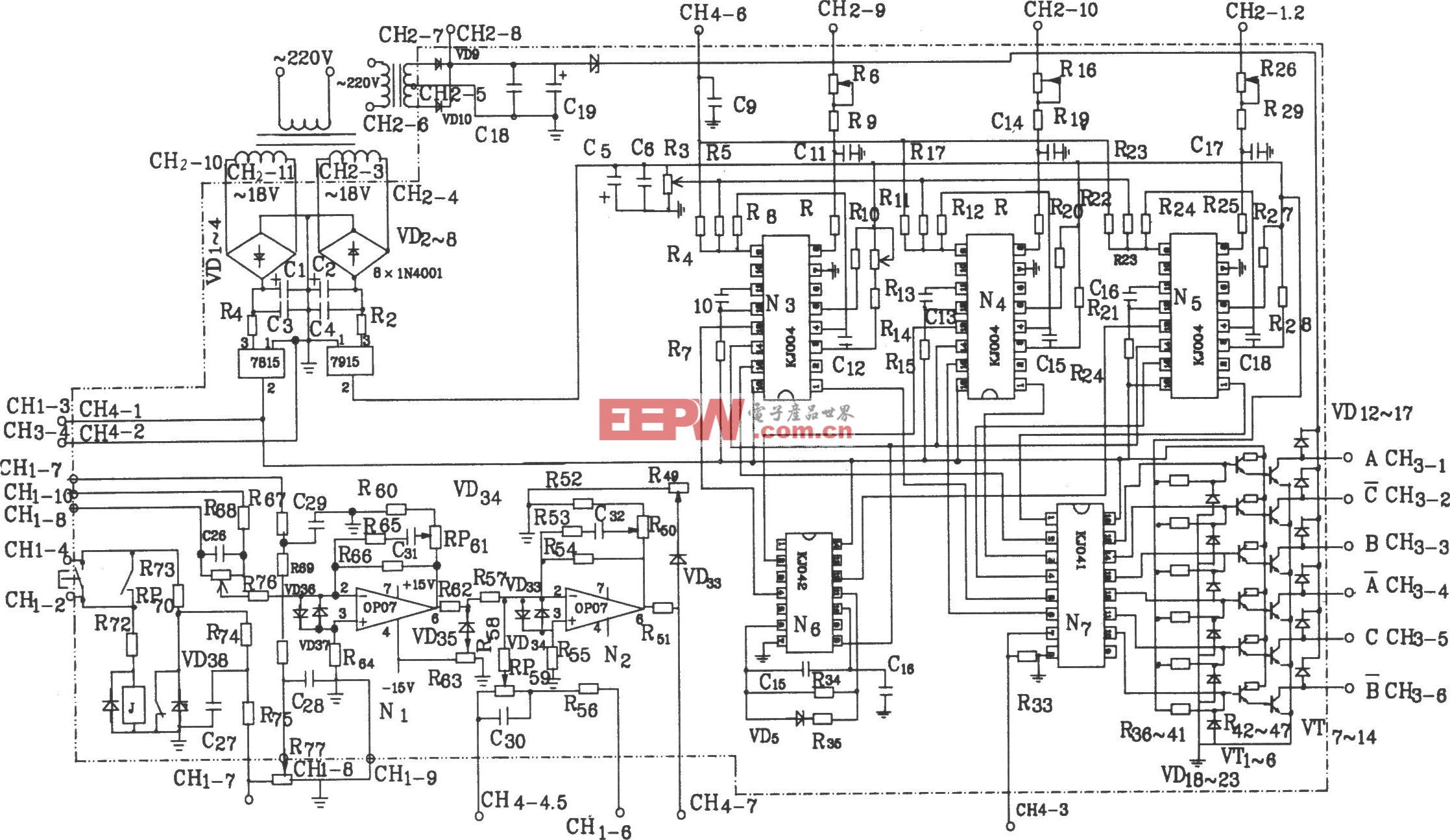

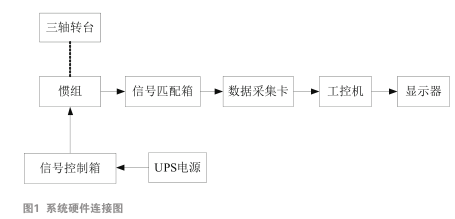

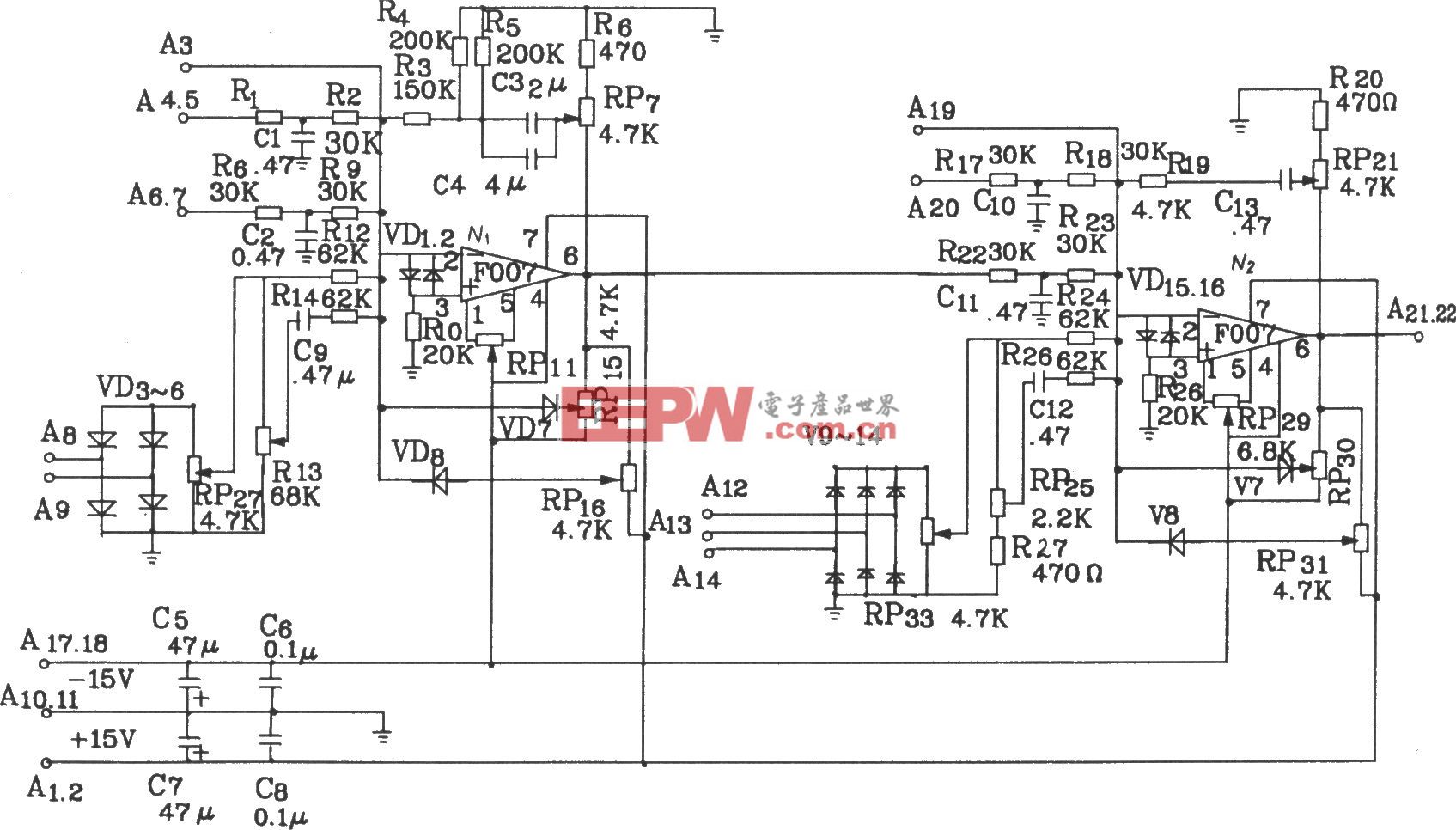

本专用数据采集控制板利用CPLD作为主控制器,统一协调通道切换与数字信号处理、实现数据采集与接口传输逻辑控制。该数据采集控制板共有四种类型的信号输入和一种开关信号量输出。图1给出其基本硬件模块组成。

利用CPLD的资源和结构特点是本设计的核心。为提高编码器输入信号的分辨细长,配套设计一个四倍频电路,并在通道后端设计一个脉冲静态计数电路,使输入信号转换为8bit信号挂接到采集板总线上。八路模拟输入信号主要依靠CPLD实现通道切换和A/D采集,采样数据也以8bit信号并行进入总线。考虑到提高计数精度的要求,对两路频率输入信号设计了一个动态计数电路,使计数值通过总线读出。I/O切换控制、EPP接口电路等都按一定的逻辑要求采用同一CPLD元件来实现。如此可使硬件电路十分简单,并有利于上位机编程实现。

2 数据接口

根据IEEE1284标准,在标准并行口(SPP)、增强并行口(EPP)和扩展并行口(ECP)三种模式中,EPP模式既具有双向数据传输功能,又具有较高的数据传输能力,且编程操作相对容易,最适合在数据采集系统中使用。

图4

根据IEEE1284标准对EPP模式的地址、数据读写操作的规定,可采用图2的逻辑结构分别实现地址写、数据写和数据读。在图2中,输入信号中的STB表示写信号,ASTB表示地址写信号,DSTB表示数据写信号;输出信号中Add_WR表示地址写信号、高电平有效,Add_WRN表示地址写信号、低电平有效,Data_WR表示数据写信号、高电平有效、Data_WRN表示数据写信号、低电平有效;Data_RD表示数据读信号。如此设计的目的是使该接口能方便地适应各种逻辑器件的操作要求。图3给出了采用MAXPLUS软件对上述逻辑信号进行仿真的操作时序波形。

EPP模式可在上位机BIOS中设置或通过写ECR寄存器直接设置(并行适配器基地址为0X378H,I/O端口地址为77AH)。

图5

3 编码器信号处理

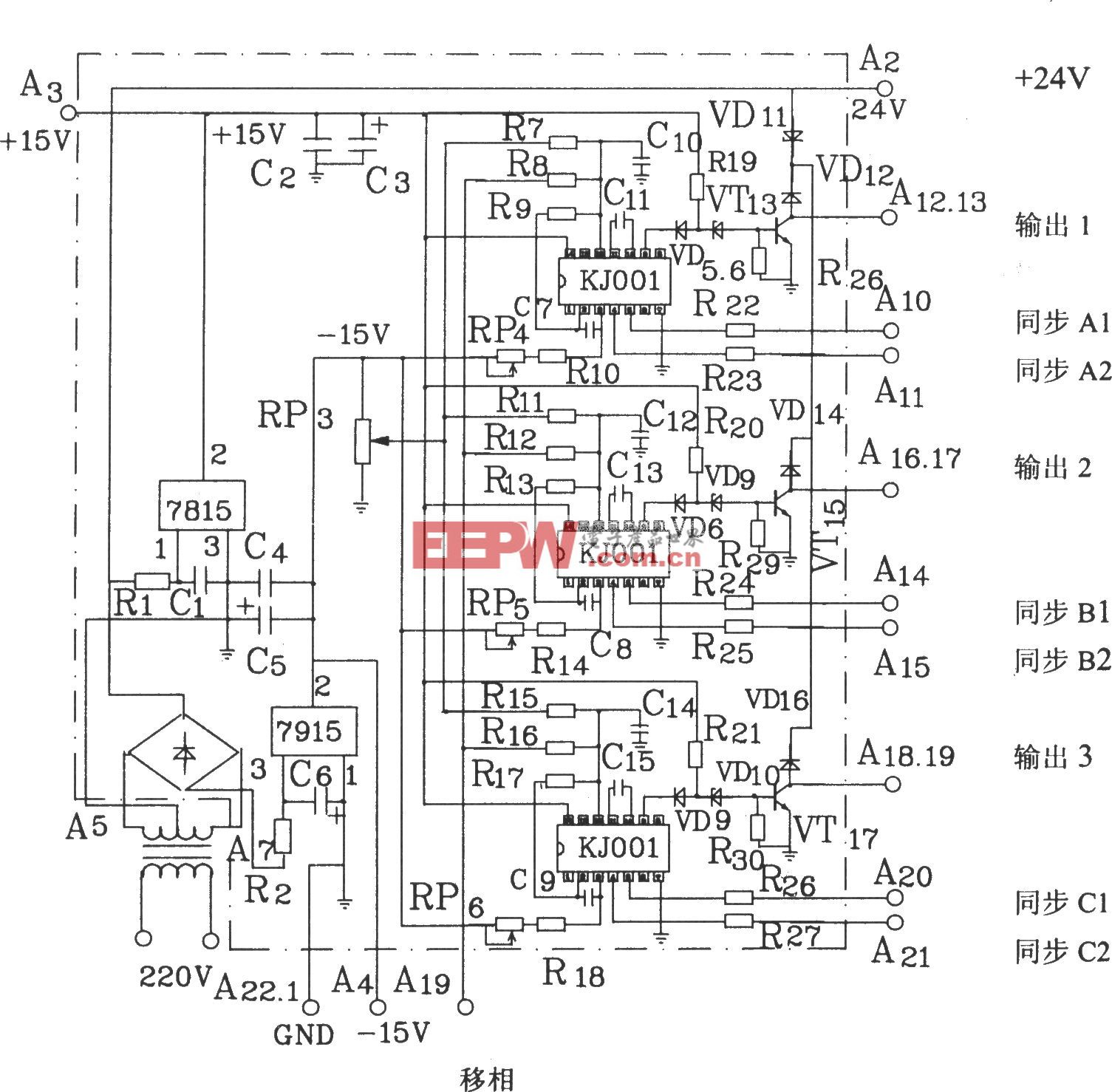

对于编码器输入信号,针对增量式光电编码器的输出具有A相、B相方波正交信号,而且二者相序取决于编码器的正反转方向,设计了一种四倍频及判向电路,如图4所示。

在图4中,CLK信号来自独立振荡源,其频率高于编码器最大输出频率四倍以上,但也不宜过高,以免导致CPLD内部结构中信号竞争等问题。INA和INB分别为编码器输入的A相信号和B相信号,CNT_UP和CNT_DN分别为输出的正转倍频信号和反转倍频信号。为保证编码器处于任何转角位置都能可靠地读出数据,编码器倍频信号最终以16bit静态计数码方式输出,CNT_UP和CNT_DN分别作为后续静态计数电路的“加”和“减”计数输入信号端。在限定转动角度≤6360情况下,对于16bit计数码,计数电路允许的最大计数值为65536,计数值可以按高低八位分两次读出。为提高编码器工作可靠性,也可以考虑进行格雷码转换。图5给出的是图4电路的信号仿真波形。

4 频率测量

对于频率输入信号,采用等精度测频方法测量频率。这种方法在实际闸门时间为被测信号频率整数倍的条件下,对被测信号计数时产生的1个字误差可以完全消除掉,并可使整个频率区域保持恒定的测试精度。

使用时为提高测量精度,基准信号CLK可以采用高精度的时钟源,因对时钟源和被测信号同步计数,计数时间长度不会影响计算结果。图7给出了等精度测频法信号仿真波形图。

图7

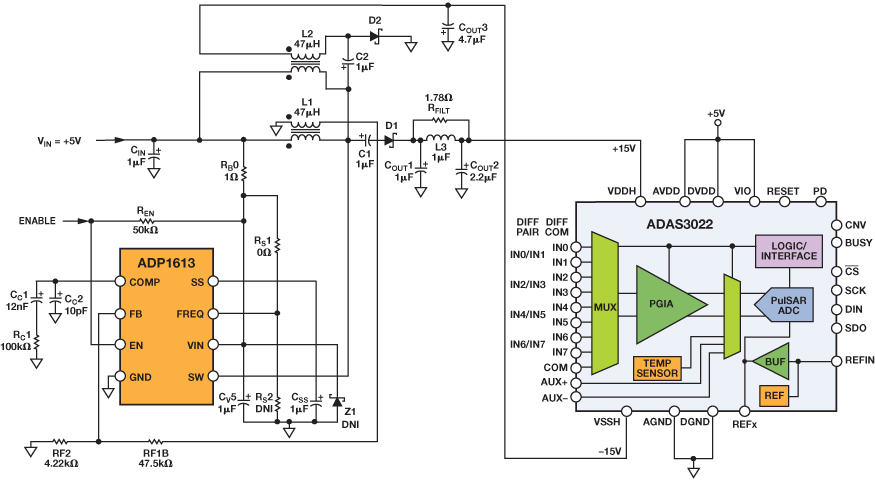

5 A/D转换器与I/O切换控制

对于模拟输入信号,采用12bit的MAX197作为A/D信号转换器。该控制字器件工作的基本过程是:首先由地址总线选通MAX197,然后通过数据总向MAX197内部寄存器写入模拟通道控制字。该控制字决定了所选的通道号、通道输入电压范围、极性以及内部或外部触发采集方式等。例如,输入电压范围为双极性、内部触发采集方式、第一通道,则应写入16进制数48H,而对第八通道则写入4FH。控制字写入后,MAX197立即启动通道转换,经过约10μs后转换完毕。转换结果放置在数据总线上,首先将其高低位切换脚HBEN置为低,此时数据总线先读取结果的低八位,再置HBEN为高,则结果的高四位放在MAX197的D0~D3口上。同时置脚INT为低,通知控制器转换完成。MAX197的转换结果用补码表示,最高位为符号位。

本系统中还具有八路开关量输入输出功能切换控制。这两种功能分别则CPLD内部的74244和74373实现。接口逻辑和如图8所示。外部接口通过光耦隔离输入输出。开关量写入的顺序是先由地址总线选通74373,然后写入相应的命令字。数据量读入与此类似。具体控制信号由EPP总线读写逻辑给出。

6 驱动软件实现

考虑到NT公司LabView环境图形化编程简例、易于实现等特点,通过设计动态链接函数库(DLL)与直接端口操作相结合实现采集板硬件驱动。在程序编制过程中,先利用VC++生成DLL,然后在LabView中使用CLF节点调用DLL。对于直接端口操作,使用LabView中的“In Port”和“Out Port”节点,对端口实现操作。当然,为使用方便起见,也可以将I/O切换控制、编码器、A/D数据采集、计数器等硬件特有功能设计成专用模块供LabView直接图形化调用。

采集控制板的上述硬件模块方案设计,可以利用适当规模的CPLD实现。此举除了成本优势外,还有体积减少、硬件集成度提高等优点,也为提高采集器可靠性创造了条件。CPLD的各种逻辑功能设计,由于有功能强大的仿真软件工具,设计过程的快速高效也不言而喻。上述设计已经在其实用测控设备中投入应用,在无板载FIFO情况下,A/D速度可以达到40kHz以上;有板载FIFO情况下,A/D速度可以达到A/D采集元件标称上限。EPP端口完全能满足板载功能模块的各类数据传输要求。通过现场反馈的情况来看,采集控制器本身的工业环境抗干扰性能和运行稳定性均表现良好。

评论