无线传感器网络SOC芯片的低功耗设计 (1)

在系统层次上,RISC CPU核设计了空闲模式及停止模式,来节省功耗。RISC CPU核进入空闲模式或停止模式时,CPU内部时钟停止运行,同时内部寄存器保持数据。

4. 结构层次上的低功耗设计

通过仔细分析整个SOC芯片的功耗来源,可知RISC CPU核,RAM,Flash及基带处理模块占去了绝大部分。下面从结构层次进行低功耗设计。

4.1 RISC CPU核的低功耗设计

微处理器的功耗降低可以通过降低频率,及降低工作电压的方法来解决。在网络节点SOC结构层次上的设计中,除了采用慢速时钟,及低电压供电的方法,还同时针对数据路径进行优化,主要目的是为了减少电路中不必要的翻转。指令译码数据路径的优化:一般情况下,CPU中所有的执行单元直接接在指令译码单元后面。一旦有新的译码数据输入,与其相连的所有执行单元电路也去进行翻转,造成不必要的功耗浪费。所以,在不影响时序功能的情况,设计分离的内部总线,将不执行的单元输入数据及控制信号锁存,其输入信号保持不变,动态功耗可以减少。芯片内部集成了RAM及Flash ROM。为了降低这两者的功耗,避免不必要的翻转,内部总线与RAM,Flash 的接口单元设计锁存器,这样的话,只有CPU访问相应的地址时,RAM及Flash内部才进行翻转。

4.2基带处理模块的低功耗设计

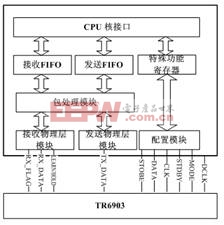

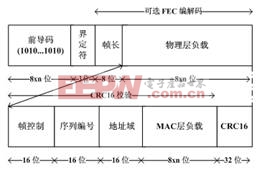

基带处理模块的设计框图如图 2所示;其基于IEEE 802.15.4协议的物理层帧及数据链路层帧结构如图 3所示。从提高cpu的效率和减少功耗角度出发,基带处理模块采用中断方式与CPU通线。基带处理模块发送完接收FIFO的数据帧,向CPU申请发送中断,等待CPU写入新的数据到发送FIFO;当基带处理模块接收到TR6903模块发来的数据帧,存放入接收FIFO中,产生接收中断等待CPU处理。

图 2 基带处理模块结构框图

图 3 物理层及数据链路层帧结构

基带处理模块主要采用并行结构与流水线技术来降低功耗。发送功能与接收功能的物理层发送模块,缓冲区都是并行结构。配置模块也是分开来设计,数据的处理方式也是并行。包处理模块的中CRC16也是采用并行结构进行校验的。这样设计的好处,是为了在慢时钟频率下,通过并行设计提高性能,达到与高速时速一样的性能。在图 2中的各子模块与子模块之间都有流水级,也就是锁存器,不仅仅为了减少不必要的翻转,更重要的减少关键路径上的长度,从而达到间接降低功耗的目的。

基带处理模块低功耗结构设计如下:

评论