基于BM算法的BCH码的译码硬件实现

3 硬件设计与实现

3.1 基于幂次的运算方式

对表1进行简化,得到表2和表3:本文引用地址:http://www.eepw.com.cn/article/192083.htm

将运算步骤都建立在域元素幂次运算的基础上,流程图中的“*”,“/”,“+”运算方式都会改变。例如:(1110)*(1111)mod(10011,这个为本原多项式)=1011010mod(10011)=0101,转化成幂次后(1110)*(1111)→a12*a11=α23=α8,原来二进制乘除法电路变为简单幂次的指数加法电路。“+”由原来的模二加运算变成两次查表和一次模二加运算,例如,α12+α11→查表二(1l11)+(1110)=000l→查表三0001对应α0,所以得到α12+αll=α0。在硬件实现中,表2,表3的第二列作为内容存在FPGA的ROM中,第一列作为他们的地址。

3.2 整体译码结构设计

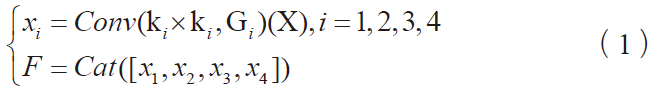

以上是BCH译码器的整体结构模块图,分四个模块,下面介绍这四个模块的功能:

(1)S_produce:根据接收码字R(r0 r1 r2…r14),产生伴随式S(s1,s2,s3,s4,s5,s6);

(2)dr:根据伴随式S(s1,s2,s3,s4,s5,s6),产生位置差错式D(dl,d2,d3);

(3)chien:以钱搜索的方式,根据位置差错式D(d1,d2,d3),产生错误图样E(e0,el,e2…e14);

(4)shift_register:同步时钟的功能,满足chien产生e14时,r14恰好输出:c14=r14+e14。

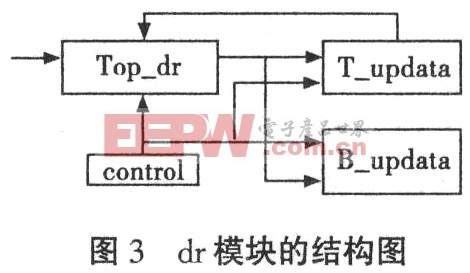

整个结构中,dr这个模块最为复杂,对应整个BM算法。图3是dr模块图。![]() 计算的功能,并将计算得到的△r值和前一状态的D(dl,d2,d3)传给T_updata,和B_updata这两个模块;B_updata完成B(x)更新的功能(B(x)一xB(x)或B(x)一△-1nd(x)),将值传给T_updata;T_updata完成T(x)更新的功能(T(x)=d(x)一△rxB(x)),并将计算结果反馈给top_dr,作为当前状态的D(dl,d2,d3);control模块完成控制整个模块的时钟同步。

计算的功能,并将计算得到的△r值和前一状态的D(dl,d2,d3)传给T_updata,和B_updata这两个模块;B_updata完成B(x)更新的功能(B(x)一xB(x)或B(x)一△-1nd(x)),将值传给T_updata;T_updata完成T(x)更新的功能(T(x)=d(x)一△rxB(x)),并将计算结果反馈给top_dr,作为当前状态的D(dl,d2,d3);control模块完成控制整个模块的时钟同步。

4 仿真结果

我们选用了Xilinx公司的xc4v1x60,仿真环境是xilinxISE6.0,moddsim SE 5.5e,在布线后的时序报告中得到的系统可以在70MHz的时钟上对信号进行实时的处理。在时序仿真中我们选用了50MHz的时钟,连续输入两帧数据(每帧数据15bit),一帧是正确的码字(100010100110l1),一帧是错误的码字(10001010001111),普通算法在延迟23个时钟周期后输出结果,简化算法在延迟20个周期后输出结果。根据译码速度计算公式:译码速率=(帧长*系统频率)僻码一帧所需要的时钟周期数,则两种算法的译码速率分别为32Mbps,37Mbps。

5 结论

在本文中我们利用FPGA实现了基于BM迭代译码算法的BCH码译码器,并根据FPGA块ROM资源充足的的优势,采用基于幂次的运算方式,合理地对.BM流程算法进行模块划分,同时实现了简化的BM算法,缩短了译码延迟,提高了整个译码器的译码速度。计算机仿真结果表明,本设计所实现的BCH译码性能基本满足传输要求,为后续长BCH码的硬件实现作了较好的铺垫。

评论