成功解决FPGA设计时序问题的三大要点

从图4可以看出在FPGA的管脚上,PCB传播延迟与时钟(CQ_FPGA)和数据(Q_FPGA)信号间的关系。在TimingDesigner软件的动态链接参数表中使用单独的变量可以轻松地获得PCB板的延时及延迟值对相关的信号的影响。现在,我们可以在适当的FPGA装置中,为获取时钟而得到内部布线延迟和确定正确的相位偏移。

FPGA设计要素

大多数的FPGA利用约束驱动进行布局和布线。时序约束为关键信号提供时序信息。TimingDesigner软件提供独特的时序参考图如测量和计算变量结果,从行内文字到文件都支持厂商特定的约束语法。例如,在一个FPGA约束布线中,对符合其动态文字窗口的语法要求中,可以通过时序图中为特定信号计算延迟误差。然后,我们可以将这些语法通过一个文本文件导入到FPGA的开发系统中,或者我们可以直接将数值复制到FPGA的约束编辑器中。

对于高速存储器接口设计,数据存储器被放置在FPGA装置I/O单元的附近,以尽量减少布线延时的影响。该I/O单元只有一个布线路径为输入数据信号,因此在数据总线的每一部分都存在数据路径延迟。FPGA的PLL也被用来进行适当的时钟控制,并通常有几种可能的从输入焊盘到捕捉寄存器的路径。制造商通过控制特定的属性,使PLL的特点包括相位偏移,相乘,或相除等因素,无论是原始示例的设计代码或约束都可以带入模块。因此,时钟和数据路径的布线和延误必须确定,以实现适当的时钟相位偏移。

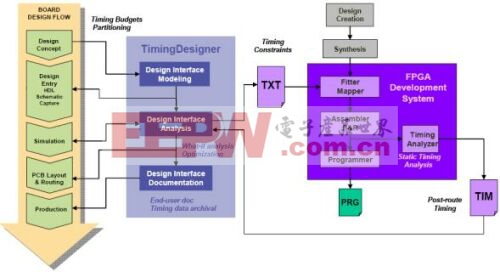

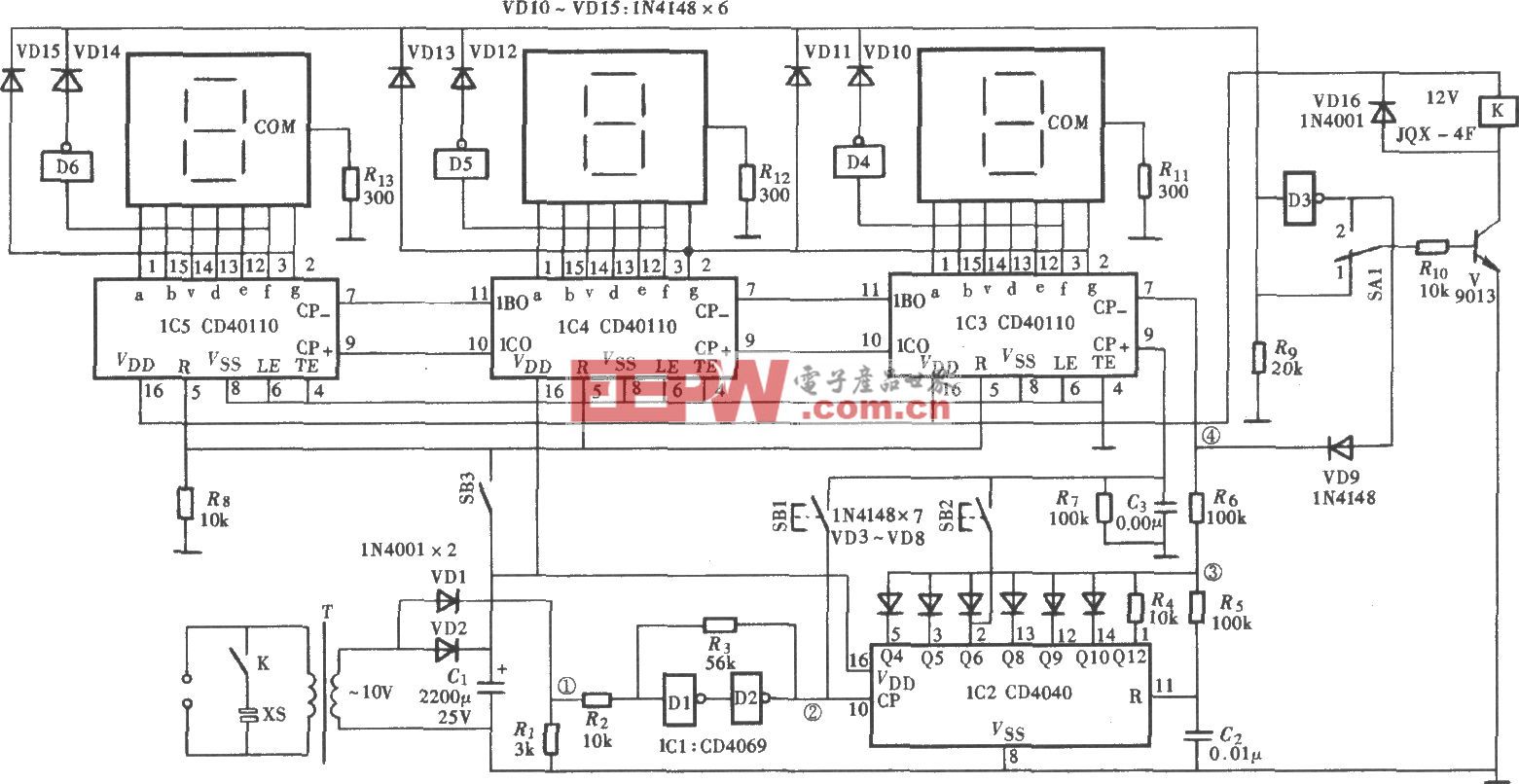

图5:TimingDesigner软件为FPGA设计流程提供直观的界面。

在FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner软件可以提取相关信息和利用图表更新。在这个设计实例中,我们需要输入数据总线和相关时钟信号的时序报告。

1.导入布线后的时序到TimingDesigner软件中

导入FPGA的时序报告信息,我们需要规划最坏的情况从而确定在图表(Q_FPGA)中相关的波形图。信号设计规范定义在同一个时序图表中不能带有同名的波形图。通过规划端口, TimingDesigner软件可以过滤时序报告并提取有用的信息。这些规划被存储在图表文件内并可预先解决的布局和布线问题。

评论