PCB上FPGA的同步开关噪声分析

如今CMOS技术让一块FPGA器件可以拥有多个I/O接口。同时,近几年,低功耗已开始成为高速I/O接口的主流概念。降低功耗最有效的途径就是降低电压,而电压降低就会导致I/O接口所允许的噪声余量变小。因此,对FPGA用户而言,量化芯片、封装和PCB环境下的系统级同步开关噪声(SSN)就显得十分必要。

本文引用地址:http://www.eepw.com.cn/article/192038.htm本文对SSN进行了系统性介绍,着重介绍由FPGA输出缓冲导致的SSN。这种噪声一般被称作同步开关输出噪声(SSO),与输入缓冲导致的SSN不同。本文介绍了系统级SSO的成因,并提出了一种分层的系统级SSO建模方法。同时,本文还讲解了如何将SSO模型与频域和时域测量相关联,并给出了几种减小SSO的PCB设计方法。

系统级SSO的形成机制

带FPGA的PCB是一个复杂的系统,可将其分为包含有源电路的晶片部分、带有嵌入式无源器件的支撑走线的封装部分,和为FPGA与外部提供连接的电路板部分。在此类系统中,要想弄清芯片内部的噪声特性很困难。因此,对与FPGA相连的PCB走线近端和远端的SSO进行量化就显得很有价值。造成SSO的主要有两大因素:电源分配网(PDN)的阻抗和开关I/O之间的互感耦合。

从系统的角度来说,PDN中包含晶片级、封装级和板卡级的组件,这些组件共同为CMOS电路供电。当一定数量的CMOS输出驱动电路同时打开时,就会有很大电流瞬间涌入PDN的感性电路元件中,从而产生一个delta-I压降。互连结构产生寄生电感,例如球栅阵列封装上的电源焊球和PCB中的电源过孔。这种快速变化的电流还会在电源/接地平面对之间激励起放射状的电磁波,电磁波从PCB的平面边缘反射回来,在电源/接地平面之间产生谐振,从而导致电压波动。

造成SSO的另一个重要原因是互感耦合,尤其是在芯片封装/PCB边沿周围产生的互感耦合。芯片BGA封装上的焊球与PCB上的过孔都属于紧耦合的多导线结构。每个I/O焊球及其相应的PCB过孔与离它最近的接地焊球和接地过孔构成一个闭合环路。当多个I/O口的状态同时发生变化时,会有瞬态I/O电流流过这些信号环路。这种瞬态I/O电流又会产生时变的磁场,从而侵入邻近的信号环路造成感应电压噪声。

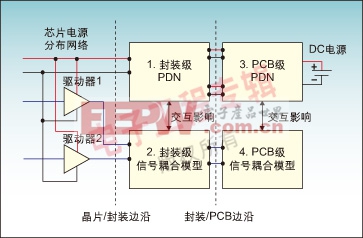

一个优秀的SSO模型应能体现SSO的基本形成机制。图1给出的就是一个用于预测PCB中SSO的分层模型。在晶片一级,我们需要的是能在有限复杂度下提供电源线和信号线上精确电流分布的输出缓冲模型。在封装一级,为简单起见,可利用建模工具分别得到PDN模型和信号耦合模型,但应谨慎考虑PDN和信号耦合模型之间的相互影响。这两个模型起着桥梁的作用,连接了芯片封装上凸点端的输出缓冲模型和焊球端的PCB级模型。PCB的PDN模型通常包含电源/接地平面和其上的大容量/去耦电容,而PCB的信号耦合模型中则包含一个紧耦合的过孔阵列和不同信号层上的松耦合信号走线。这两个PCB级模型的交互效应出现在PCB过孔阵列中,感性串扰正是从这里将噪声带入PDN模型,delta-I噪声反过来会降低I/O信号质量。这种分层建模方法合理地保持了仿真精度,同时也提高了此类复杂系统的计算效率。

图1:带FPGA的PCB的SSO模型示意图。

通过PCB设计减小SSO

下面针对装有FPGA的印制电路板,介绍两种基于SSO产生机制来减小SSO的基本设计方法。

1. 减小感性耦合的设计方法

评论