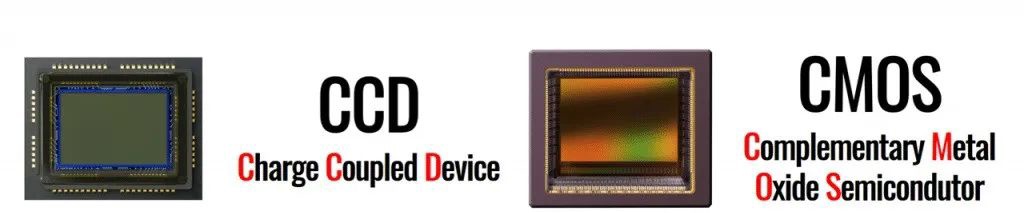

基于CPLD的全帧型CCD图像传感器驱动系统设计

光积分结束后进人第三阶段,即帧转移阶段,而帧转移又可以看成是垂直行转移和水平像素转移交替进行的,它们之间的转换通过SSC电平的高低转换实现。

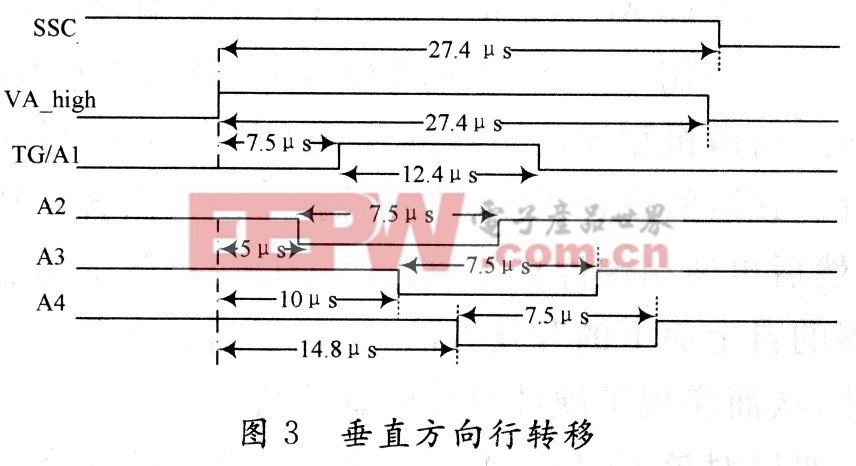

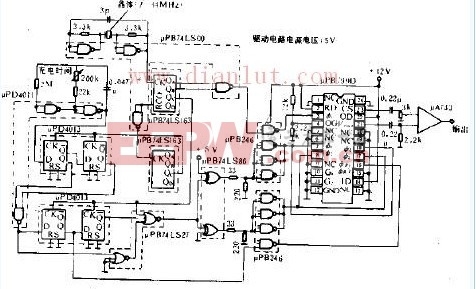

SSC上升沿的到来标志着一次水平像素转移的结束和一次垂直行转移的开始,CCD像素垂直方向的行转移是由A1,A2,A3,A4等时钟及像素传输门TG时钟来完成的,其频率都为50 kHz,且四相A时钟信号要满足严格的交迭原理。在SSC保持高电平时,如图3所示,光敏区里已经生成的电荷包在四相A时钟信号的驱动下逐行地向上和向下转移到输出寄存器。本文引用地址:http://www.eepw.com.cn/article/192035.htm

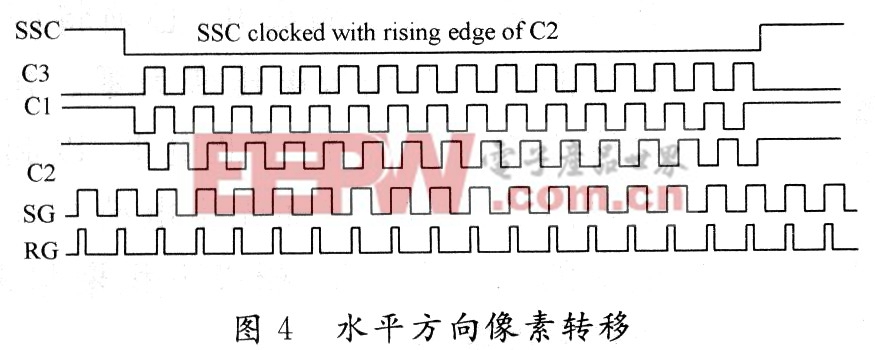

SSC下降沿到来时,标志着一次垂直行转移的结束和一次水平像素转移的开始,CCD像素水平方向像素的转移是由C1,C2,c3等时钟来完成的,信号频率都为25 MHz。其转移原理与垂直行转移原理一样,三相C时钟信号亦要严格满足三相交迭原理。如图4所示,输出寄存器就是在三相C时钟信号的驱动下将这一行逐个像素向输出放大器转移的。

RG(Reset Gate)是通过复位管对输出放大器的浮置扩散电容(Floating Diffusion Capacitante,FD)进行复位的信号,其中FD可以将接收到的电荷包转换为电压信号。复位后FD可以接收下一个电荷包。SG(Summing Gate)是在输出栅OG之前的最后一个栅,SG信号和RG信号的相位与C3信号的相位相同。一行电荷包经过输出放大器的转换和放大后,以电压信号的形式从CCD输出。接下来再进行下一行的垂直行转移和水平像素转移输出,直到将光敏面上的所有5 356行电荷包输出完毕为止。由此可见,整个一帧图像是在A时钟信号和C时钟信号的交替驱动下从CCD芯片的输出放大器输出而完成帧转移的。

2 驱动系统设计

随着大规模可编程器件的迅速发展和广泛使用,传统的通过TTL标准电路构成的积木式电路系统已经慢慢被淘汰。目前较为流行的CCD驱动电路设计方案一般有两种:一是用FPGA或者是CPLD产生CCD的时序驱动信号,以及用模拟电路(功率放大晶体管和电位器)实现对CCD的直流电平驱动信号;另一种则是用专用的CCD驱动芯片,实现对CCD的驱动。前者要求开发者对硬件描述语言熟悉,而且实现灵活,集成度高,方便功能的升级和扩展;后者则只需对寄存器进行设置,编程较为简单,但是可扩展性稍差。在此,采用Altera公司EPM7160SIC 84-10型可编程逻辑器件(CPLD),使用Altera公司的QuartusⅡ集成开发环境,并通过与微机相连的下载线实现CPLD的烧写和在线编程。顶层的设计采用原理图输入,设计出各个功能模块,然后再使用硬件描述语言(VHDL)对各个功能模块编程的自上而下的开发方法,实现了高层次复杂逻辑的设计,从而实现了硬件设计的软件化。

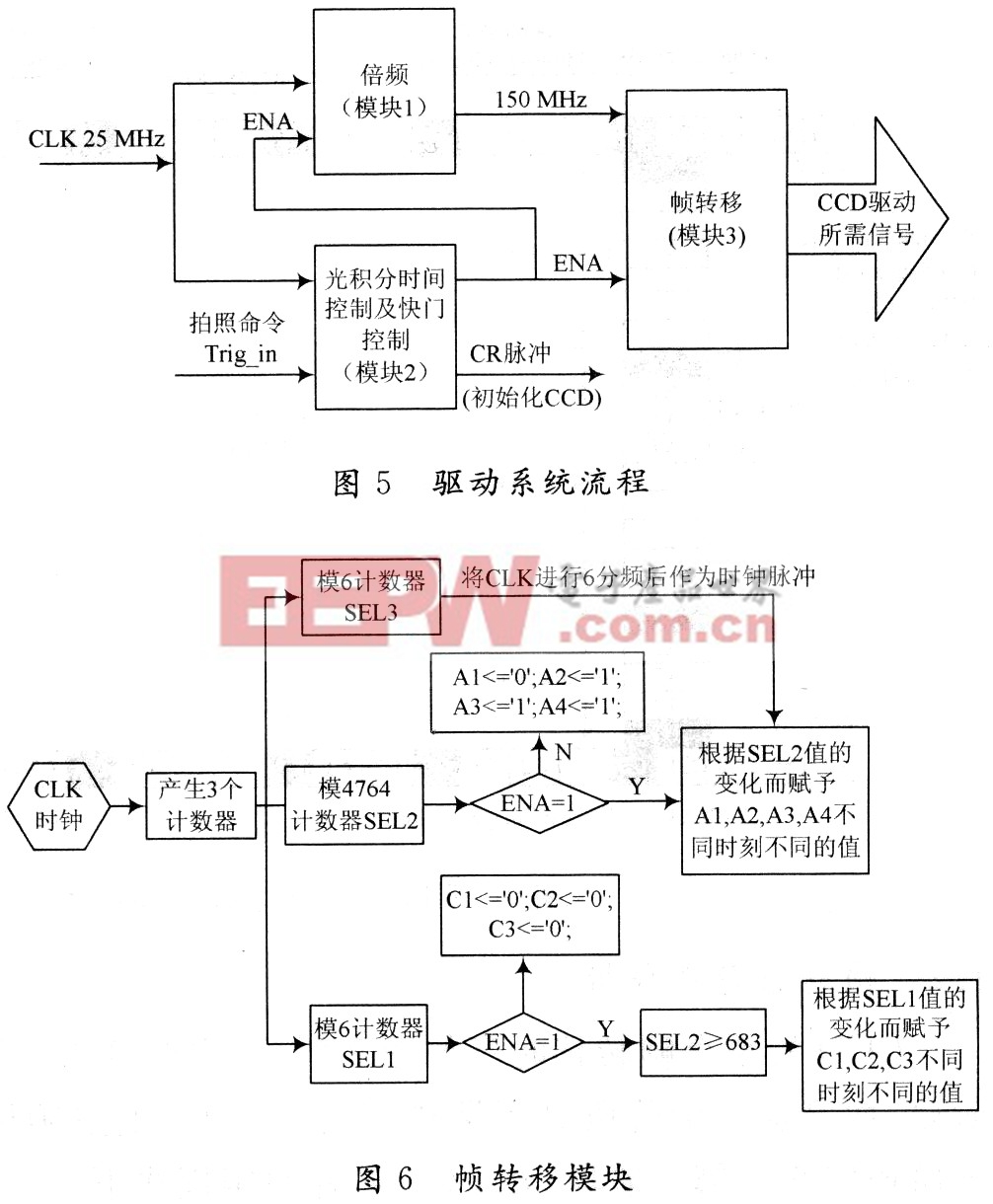

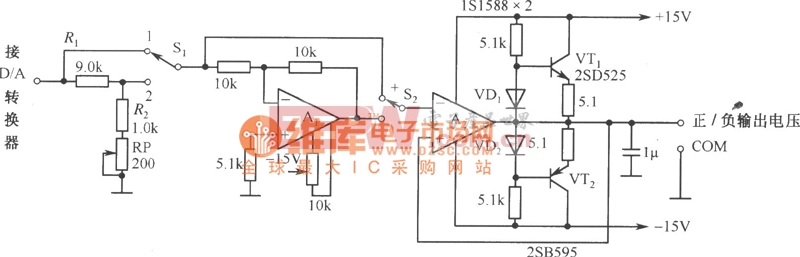

通过对该CCD芯片的了解,将顶层设计分为3个功能模块,分别为倍频模块(模块1)、光积分时间控制及快门控制模块(模块2)、帧转移模块(模块3),各功能模块的关系如图5所示。模块1为倍频模块,通过调用该模块,可产生帧转移所需的频率脉冲信号。由于CPLD芯片一般不带有PLL模块,故可采用延时加异或的方式来实现倍频。不过目前较新的CPLD,如Lattice的MachXo系列器件则可直接调用PLL,此处不再赘述。模块2为光积分时间及快门控制,通过拍照指令产生CR脉冲信号,对CCD进行初始化,并生成一个在光积分期问保持高电平的使能信号ENA。将ENA分别发送至模块1和模块3。CR信号和ENA可通过对按键信号Trig―in的延迟处理来实现,也较为简单。该设计中最关键的是帧转移模块。其原理主要是利用3个计数器进行相互嵌套,从而产生所需的驱动信号,其简易流程如图6所示。

评论