HDMI 设计指南:HDTV接收机应用中高速PCB的成功设

过孔这一术语一般指的是印刷电路板上的电镀孔。一些应用要求直通的过孔足够宽,从而能放置穿孔组件的导线,而高速电路板设计一般是在对信号层进行更改时将其作为线迹过孔使用,或将其作为连接过孔使用,以将 SMT 组件与所需的参考层相连接,同时也将同一电位的参考层相互连接(见上一章节中提及的过孔连接接地层)。

与一个过孔连接的各个层与一个过孔周围焊盘(过孔焊盘)直接相连接。不必连接的各个层由一个间隙环将其与过孔相隔开。每个过孔与接地之间都有电容,电容量可以使用如下的方程式计算出近似值:

其中,D2=接地层间隙孔的直径(内径)

D1=过孔周围焊盘的直径(内径)

T=印刷电路板的厚度(内厚)

ε1=电路板介电常数

C=寄生过孔电容 (pF)

由于电容与尺寸成一定比例增加,因此,高速设计中的线迹过孔应尽可能的小,以避免较大的容性负载导致的信号衰减。

当把一个去耦电容器连接至接地层,或将各个接地层相连接时,与其电容相比,过孔电感更为重要。该电感的数值大约为:

其中,L=过孔电感 (nH)

h=过孔长度(内长)

d=过孔直径(内径)

由于该方程式涉及到一个对数,所以改变过孔的直径并不会对电感产生任何影响。改变过孔长度,或多个过孔并联可能会使电感发生较大的变化。因此,应在每个器件的终端放置两个并联的过孔,将耦合电容器与接地连接。对于接地层之间的低电感连接而言,应在电路板上以相等的间隔放置多个过孔。

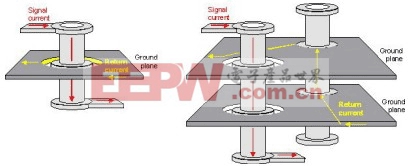

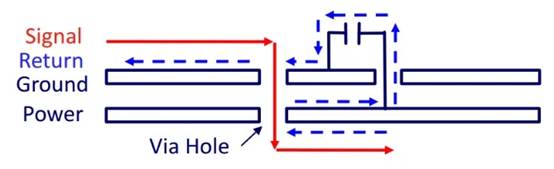

尽管强烈建议不要对高速线迹的电路层进行更改,但是如果有必要更改的话,应确保有一条连续的电流回路。图 14 的左边部分显示了用于单个电路层更改的电流回流流向,右边部分显示了用于多个电路层更改的电流回流流向。

图14 单个及多个电路层更改的电流回路

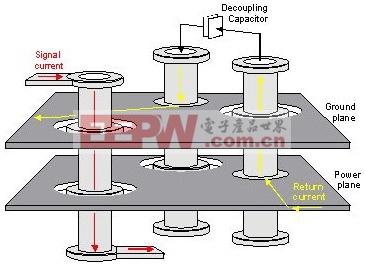

内部间隙环的一层金属层片实现了对接地层从底层到顶层的电流流向的更改。因此,当一个信号通过一个过孔,并延续至同一层的另一侧时,不存在电流回流非连续性的问题。 通过交叉多个参考层实现了从一个层至另一个层的信号线迹更改,这样使电流回路的设计复杂化。在两个接地层的情况下,一个接地到接地的过孔必须放置在信号过孔的附近,以确保获得一个连续的电流回路(见图 14 右边的图表)。如果参考层为不同电压电位,如图 15 中所示的电源层和接地层,电流回路的设计将变得较凌乱,这是由于需要第三个过孔和一个去耦电容器。电流回流开始于其最接近信号电流的电源层底部。之后流经电源过孔,通过去耦电容器流向接地过孔,最后回到接地层的顶部。

图15 单个及多个电路层更改的电流回路

放置有多个过孔和去耦电容器的电流回路具有较高的电感,因此不利于信号完整性,并增加了 EMI。如果可能的话,在进行高速布线时,避免更改各个层,这是因为这样会降低电路板性能,使设计复杂化并增加生产成本。

去耦电容器

去耦电容器为 IC 的充电提供了部分资源,该 IC 在对内部切换响应时需要大量的电源电流。不足量的去耦会导致所需电源电流不足,阻止 IC 的正常运作,从而导致信号完整性数据错误的发生。这就要求其在相关的频率范围内提供较低的阻抗。为了实现这个目的,通常的做法是均匀地分布电路板上的一组去耦电容器。除了保持信号的完整性以外,去耦电容器还充当了一个 EMC 滤波器,以阻止高频 RF 信号在整个 PCB 上进行传播。

当在电源层与接地层之间连接一个电容器时,我们实际上是在对配置有一个串联谐振电路的电源进行加载,该电路的频率取决于代表了一个真实电容器等效电路的 R-L-C 组件。图 16 显示了一个初始等效电路的寄生组件,以及其向一个串联谐振电路的转化。

图16 一个串联谐振电路模拟的电容器损耗

漏电阻 RL 表示低频情况下漏电流的损耗。RD 和 CD 表示由于分子极化 (RD) 及介电吸收 (CD) 所产生的损耗。RS 表示导线和电容器金属板中的电阻。三个电阻损耗组成一个等效串联电阻 (ESR)。在 ESR 这种情况下,等效串联电感 (ESL) 为电容器金属板及内部导线的电感之和。

请注意,尽管连接过孔的电容器的阻抗较低,但是会产生大量的串联电感。因此,应在每个电容器终端使用两个过孔来减少过孔电感。

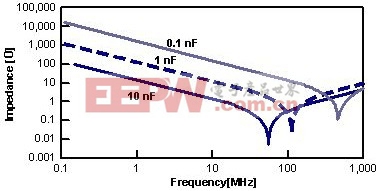

图 17 显示了电容器阻抗 (Z) 级数与一个 10 nF 电容器频率的关系。在远低于自谐振频率 (SRF) 条件下,电容性电抗占优。同 SRF 更为接近时,电感性电抗受试图中和电容性分量的影响。在 SRF 上,电容及电感电抗消失,仅有 ESR 存在。请注意,ESR 取决于频率,且与通常的看法相反,其并不会在 SRF 上达到其最小值,但是阻抗 Z 却会这样。

图17 电容器阻抗与频率的关系

并联的电容器能在一个分布式的去耦网络中运行,其原因是电容总量增加至所选用去耦电容器数值 N。并且当电容量为这一数值时,电容器阻抗由于频率低于 SRF 而有所减少。类似地,电感也会发生变化,这是因为在频率高于 SRF 时阻抗会降低。

一个可靠的去耦网络设计必须包括低至 DC 的较低频率,而 DC 需要实施大型的电容器。因此,为了能在低频情况下提供足量的低阻抗,应在稳压器的输出端,以及为 PCB 提供电源的地方放置一些 1 ¼F 到 10 ¼F 的钽电容。对于更高的频率范围而言,应在每一个高速切换 IC 旁边放置一些 0.1 ¼F 或 0.01 ¼F 的陶瓷电容。

总结

本文旨在讨论高速 PCB 设计几个主要方面。尽管已有大量技术性著作、研讨会、新闻稿和网上论坛涉及该话题,但是本文目的在于以一个全面的方式为 PCB 设计人员提供主要设计指南。

下列提出的几条建议将会有助于在最短的时间内完成符合 EMC 要求的电路板的设计。

评论