HDMI 设计指南:HDTV接收机应用中高速PCB的成功设

引言

本文引用地址:http://www.eepw.com.cn/article/192029.htm针对使用 HDMI 多路复用中继器的用户,本文提供了如何通过精心设计印刷电路板 (PCB) 来实现器件全部性能最优化的设计指导。我们将对高速 PCB 设计的一些主要方面的重要概念进行解释,并给出一些建议。本文涵盖了层堆栈、差动线迹、受控阻抗传输线、非连续性、布线指南、参考平面、过孔以及去耦电容器等内容。

层堆栈

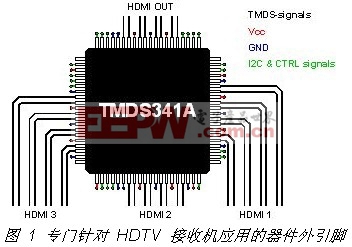

HDMI 多路复用中继器的外引脚是专门针对 HDTV 接收机电路中的设计(见图 1)而量身定制的。封装的每一侧都提供了一个 HDMI 端口,具有四个差动 TMDS 信号对,从而实现三个输入端口和一个输出端口。剩余信号由电源轨、Vcc 和接地以及低速信号(例如:I2C 接口、热插拔和多路复用选择器引脚)组成。

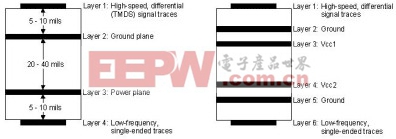

完成一个低 EMI PCB 设计最少需要四层堆栈(见图 2)。层堆栈应按照下列顺序(自上而下):TMDS 信号层,接线层,电源层和控制信号层。

图2 建议在一个接收机 PCB 设计中使用 4 或 6 层堆栈。

在顶层上对高速 TMDS 线迹布线可以避免使用过孔(及其电感),并且允许从 HDMI 连接器至中继器输入以及从中继器输出至后续接收机电路的干净互联 (clean interconnect)。

在高速信号层的下面放置一个坚实的接地层,这样就可以为传输线路互联建立一个受控阻抗,并为返回电流提供一个优异的低电感通路。

在紧挨接地层的下方放置电源层可以创建额外的高频旁路电容。

在底层布线低速控制信号可实现更大的灵活性,因为这些信号链通常拥有允许非连续性(如过孔)的裕度。

如果需要一个额外电源电压层或信号层,那么就应添加一个二级电源层/接地层系统至该堆栈,以使其保持对称。这样就可以使堆栈保持机械稳定,并防止其变形。每个电源系统的电源层和接地层均可以被紧密地放置在一起,从而大大增加高频旁路电容。

差动线迹

HDMI 使用转换最小化差分信令 (TMDS),用于传输高速串行数据。差分信令为单端信令带来了极大的好处。

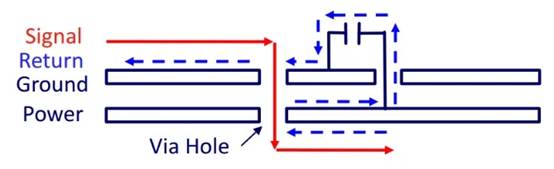

在单端系统中,电流通过一个电感从电源流至负载,并经由一个接地层或线路返回。该电流引起的横向电磁 (TEM) 波会自由地向外部环境辐射,从而引起严重的电磁干扰 (EMI)(见图3)。而且,电感中的外部源噪声不可避免地被接收机放大,从而破坏信号完整性。

替代差分信令要使用两个电感,一个用于正向电流,另一个用于电流返回。因此,当紧密耦合时,该两个电感中的电流为等量,但是极性却相反,并且其电磁场消失。现在,电磁场被“抢走”的两个电感的 TEM 波均不能向环境中辐射。只有在电感环路外部有极小的边缘磁场时才会发生辐射,从而产生极低的 EMI(见图3)。

图3 来自单个电感周围大散射磁场和差动信号对紧密耦合电感环路的外部小散射磁场的 TEM 波辐射

紧密电耦合的另一个好处是,感应至两个电感的外部噪声均以等量共模噪声的形式出现在接收机输入端上。具有差动输入的接收机均只对信号差异敏感,而对共模信号不敏感。因此,该接收机抑制了共模噪声,并保持了信号完整性。

为了使差分信令可以工作在一个 PCB 上,一个差动信号对的两个线迹间距必须在整个线迹长度上保持一致。否则,间距变化就会引起磁场耦合不平衡,从而降低磁场消除的效果,造成 EMI 增加。

除了更大的 EMI 以外,电感间距的变化也会引起信号对差动阻抗的变化,从而造成阻抗控制传输系统的中断,进而造成破坏信号完整性的信号反射。

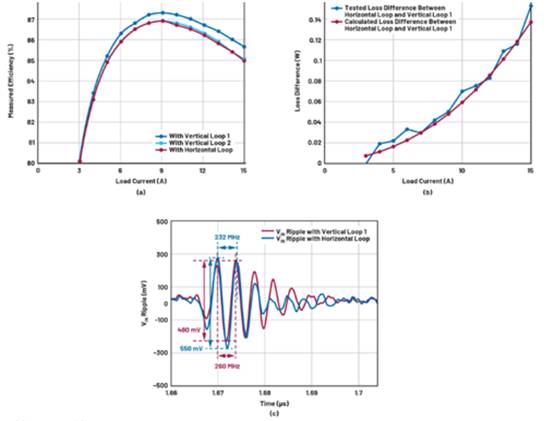

除了间距一致以外,两个电感均必须为相等的电气长度,以确保其信号在相同时间到达接收机输入端。图 4 显示了相等及不同长度线迹的逻辑状态改变期间一个差动对的“+”和“”信号。

图4 不同电气长度的线迹会引起信号间的相移,从而产生导致严重 EMI 问题的差动信号

对于相同长度的线迹而言,两个信号相等且极性相反。因此,它们的和必须为零。如果这些线迹的电气长度不同,那么较短线迹上的信号就会比较长线迹上的信号较早地改变状态。在此期间,两个线迹均驱动电流至相同方向。由于往往会作为返回通路的长线迹继续驱动电流(“早”驱动电流),因此短线迹必须找到其经由一个参考层(电源层或接地层)的返回通路。

当将两个信号相加时,该总信号在过渡相期间从零电平转移。在高频条件下,这些差动信号以大幅急剧瞬态的形式出现,其显示在接地层上,从而引起严重的 EMI 问题。

需要注意的是,“噪声”脉冲的宽度同两个信号间的相移相等,并可以被转换成一个给定频率的时间差。该时间差(也称为对内时滞)由 HDMI 规定,用于 225 MHz TMDS 时钟速率 0.4 TBIT 的接收机,其将转换为 178 ps 最大值。对于一个 HDMI 发送器而言,该规范要求 0.15 TBIT,以用于 225 MHz 的 TMDS 时钟速率,其将转换为66 ps最大值。

评论