基于CPLD的VGA视频显示系统的设计

视频DAC模块

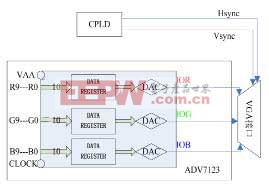

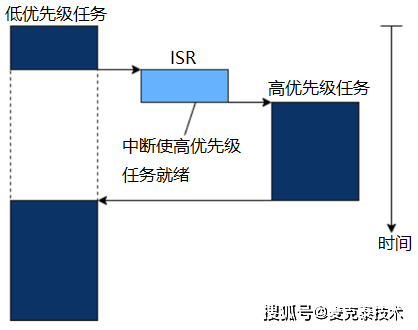

ADV7123是一个三路10位输入的高速视频DAC,具有330MHz的最大采样速度,与多种高精度的显示系统兼容,包括RS-343A和RS-170,可以广泛应用于如HDTV、数字视频系统(1600*1200 @100Hz)、高分辨率的彩色图片图像处理、视频信号再现等,因此能够满足多方面应用需求。视频DAC(ADV7123)工作原理如图3所示。

图3 ADV7123工作原理

CPLD提供Hsync(行)、Vsync(场)同步信号,直接接入15针的VGA显示接口连接器。在点时钟脉冲pixel clock的作用下将3路10位的RGB信号送入数据寄存器,而后送到3个DAC模块,复合消隐信号和复合同步信号加到红、绿、蓝模拟信号送到输出端。

系统软件设计

系统软件设计是本文的重点,主要包括三部分内容:SRAM读写状态机的设计、CPLD与SRAM的缓冲模块通信以及VGA时序设计。

SRAM读写状态机的设计

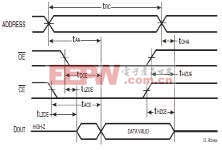

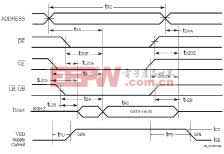

以6416为核心的图象处理机通过外部存储器接口向外传送数据,连接到后端的显示系统;但SRAM需要严格的通信时序确保数据的完整性,此处在CPLD内部通过状态机构造SRAM的读时序和写时序,确保了6416能够和SRAM正常通信,也确保缓冲模块的正常运行。读写SRAM的时序图如图4和图5所示。

图4 读周期时序图

图5 写周期时序图

当从SRAM中读取数据时:首先使能片选;UB、LB时钟处于有效状态;WE为高,时钟处于无效状态;主要由OE的时序来控制使其符合读时序图,才能正确地读出存储器中的数据。在向SRAM中写入数据时,同样首先使能片选;UB、LB时钟处于有效状态;OE为高,时钟处于无效状态;主要由WE的时序来控制使之符合写时序图,才能向存储器正确写入数据。

CPLD与SRAM组成的缓冲模块的通信

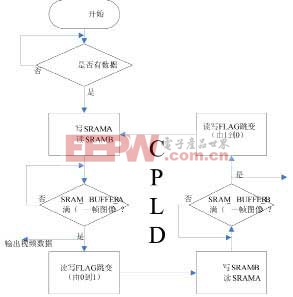

CPLD与SRAM组成的缓冲通信模块,即如何乒乓读写SRAM机制。设定一个读写标志FLAG,当一块SRAM写满一帧图像时,FLAG会出现“1”到“0”或者“0”到“1”的跳变,同时切换数据流的流向,写另一块SRAM,同时切换输出至后级DAC的数据流;如此循环,软件流程图如图6所示。

图6 缓冲模块通信软件流程图

评论