基于Verilog HDL的DDS设计与仿真

可见,理论上通过设定DDS相位累加器位数N、频率控制字X和基准时钟fc的值,就可以得到任一频率的输出。

本文引用地址:http://www.eepw.com.cn/article/192002.htm频率分辨率为:fres=fc/2N,由参考时钟和累加器的位数决定,当参考时钟的频率越高,相位累加器的位数越高,所得到的频率分辨率就越高。

1.3 方案的选择

在利用FPGA制作DDS时,相位累加器是决定DDS性能的一个关键部分。一方面可以利用进位链来实现快速、高效的电路结构,同时长的进位链会减少其他逻辑的布线资源,限制整个系统速度的提高;另一方面可以利用流水线技术提高工作频率,但系统频率转换速度会相对降低。在选择累加器实现方案时需要综合考虑。

正弦波查询表ROM也是制作的重点。在FPGA中ROM表的尺寸随着地址位数或数据位数的增加呈指数递增,如何在满足性能的前提下节省资源开销。一方面通过相位累加器的输出截断方式,例如从32位的相位累加器结果中提取高16位作为ROM的查询地址,由此而产生的误差会对频谱纯度有影响,但是对波形的精度的影响是可以忽略的;另一方面可以根据信号周期对称性来压缩ROM的尺寸,这时系统硬件设计复杂度会有所增加。因此,需要选取合适的参数和ROM压缩技术,在满足系统性能的前提下使得系统尽量优化。

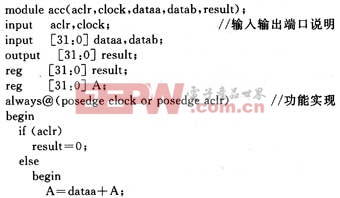

2.1 相位累加器

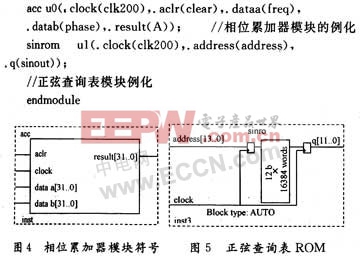

上述为相位累加器的Verilog HDL功能实现,其中数据宽度为32位。同时利用QuartusⅡ进行波形仿真见图3。对应的模块符号见图4。

2.2 ROM正弦查询表

根据DDS的原理,将正弦波形的量化数据存储于波形查询表ROM中,即可完成正弦波发生的功能。Altera公司提供了LPM ROM(ROM兆函数),这里只需借助Matlab生成.mif文件,并加载到LPM ROM中即可得到所需的正弦查询表ROM。

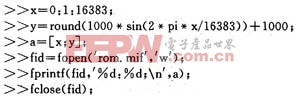

在Matlab中,运行下面的语句可以得到储存正弦波数字幅度值的.mif文件。例如产生214×12 b的正弦波0~27π幅度值,语句如下:

由此而生成的rom.mif文件内容是正弦波0~2π数字幅度值,但是格式不符合.mif。文件的格式,需要对其进行修改。.mif文件的格式如下:

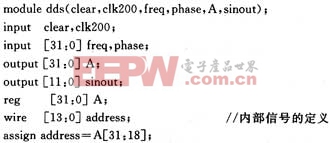

这样通过例化LPM ROM得到了正弦波查询表ROM的模块,地址宽度为14位,输出数据为12位。模块符号见图5。

2.3 DDS顶层模块的实现

评论