级联信号处理器的FPGA实现

3 FPGA仿真

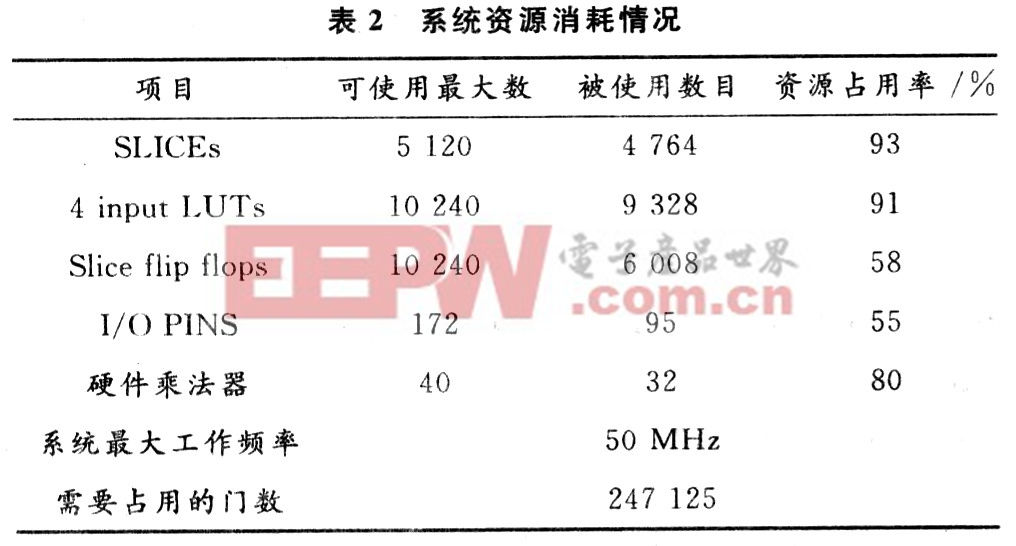

系统利用FPGA实现了一个32阶的级联型信号处理器,选用的FPGA芯片是XILINX公司的集成了18×18位硬件乘法器的VirtexⅡ系列的XC2V1000-5-FG256,其资源消耗情况如表2所示。本文引用地址:http://www.eepw.com.cn/article/191993.htm

为了方便仿真和结果观察,选用固定值输入,图4(a)和图4(b)分别是系统级联型工作模式及系数切换仿真和系统单片工作模式仿真结果。

从图4(a)和图4(b)可以看出,系数寄存器和内部控制寄存器可以正确读写,当输入系数切换指令后,系数正常交换,整个系统工作正常。

4 性能分析

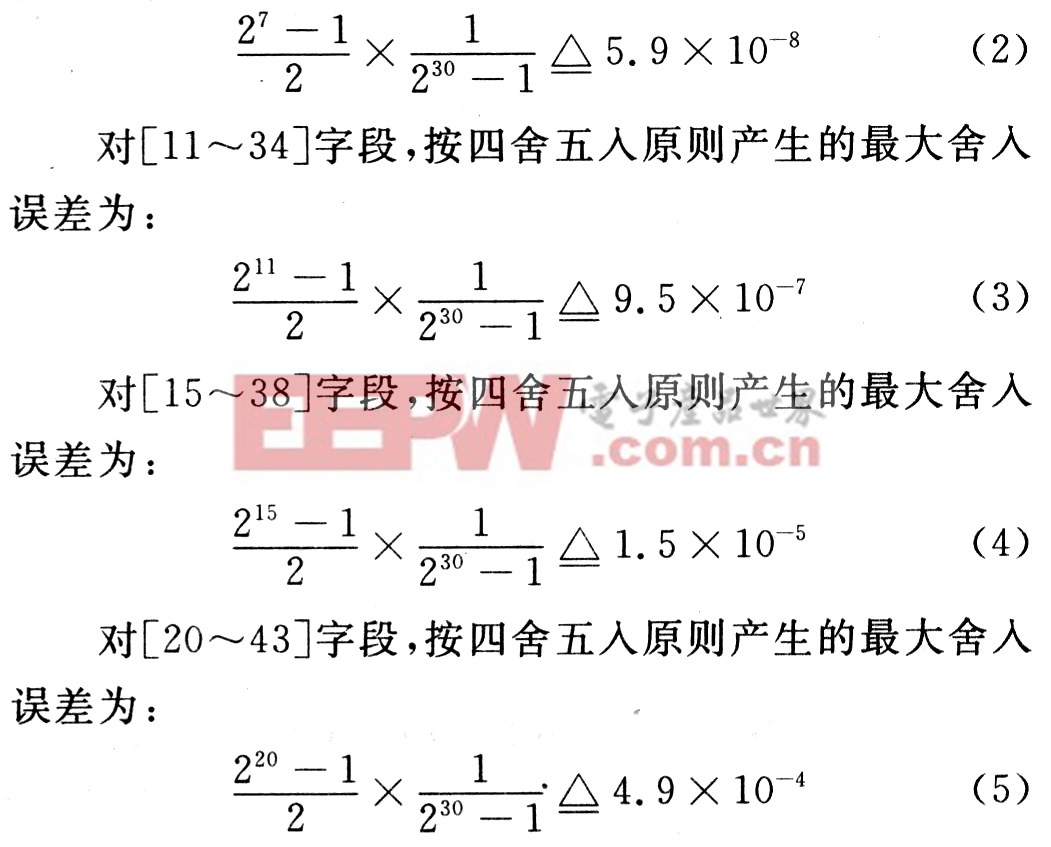

系统的输入数据和系数都是16位的二进制补码,所以中间结果的[0~30]字段对应着-1~+1。而系统的中间结果是以满精度运算的,所以系统输出的误差产生于数据选择单元,四组字段会产生不同的误差。

对[7~30]字段,按四舍五入原则产生的最大舍入误差为:

系统的仿真结果和性能分析都表明,系统可正常工作,且最高工作时钟可达到50 MHz。

5 结语

讨论了级联型信号处理器的FPGA高效实现,通过系统论证、仿真和硬件调试证明,设计方法正确有效,系统功能实现正常且稳定,为FIR滤波、快速傅里叶变换、自适应滤波等应用提供了一条可行之路,其性能可以随着可编程逻辑器件的发展而不断提高。

评论