级联信号处理器的FPGA实现

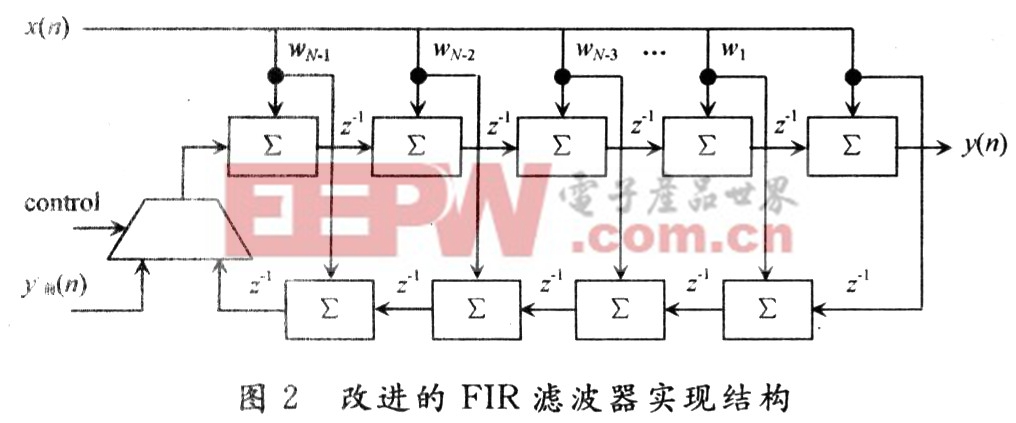

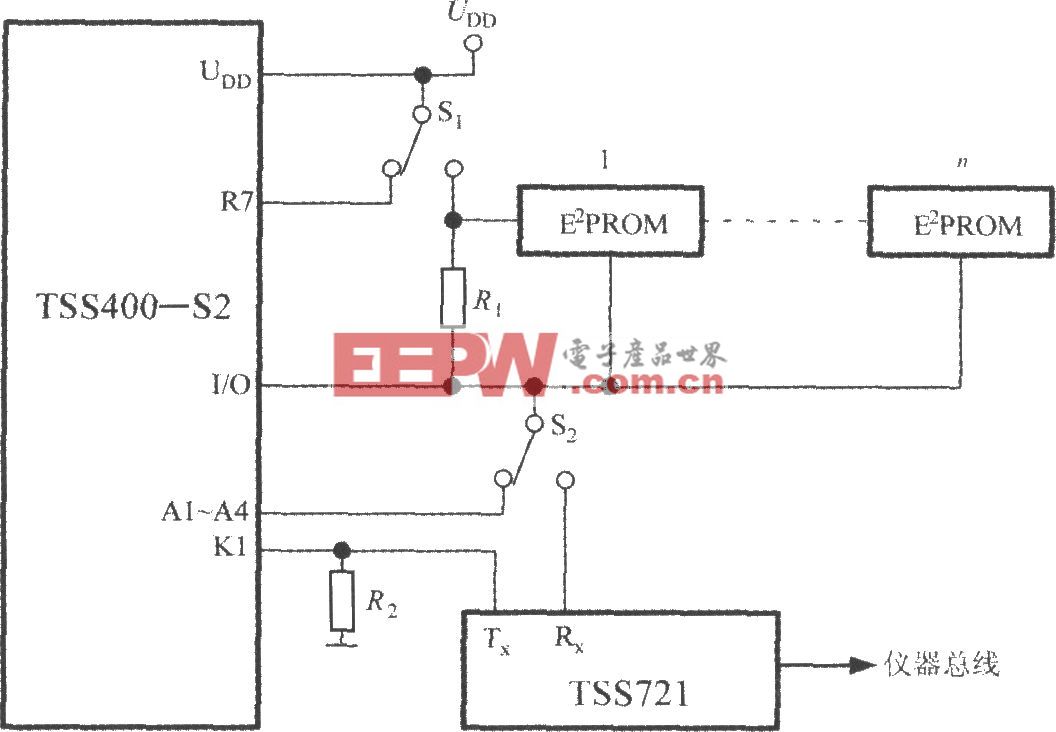

考虑到FIR滤波器系数的对称性,在横向滤波器的转置结构中再加入一条反向相加、延时支路,把单片FIR滤波器的级数由N扩展到2N,适合于阶数M为NM≤2N的滤波器使用。系统只需用一个信号便可实现对芯片级联使用或单片使用的控制,具体实现结构如图2所示。本文引用地址:http://www.eepw.com.cn/article/191993.htm

为了让设计的信号处理器能用于自适应信号处理、快速傅里叶变换等领域,还必须使系统能根据用户的要求实时改变当前系数。一般有两种方案可以实现:一是通过一个写入端口直接修改当前系数;二是准备多组备用系数,并可以在与系统工作时钟异步的情况下对这些备用系数进行修改。方案一可以节省一定的系统资源,但对一组当前系数的修改需要较长时间,且此段时间内系统无法正常工作,故实时性较差;方案二虽然消耗了较多的系统资源,但系统能在准备系数(即修改备用系数)时正常工作,修改当前系数只需将当前系数和备用系数交换,交换系数的过程只需一个时钟节拍即可完成。综合考虑各方面因素,方案二具备更好的系统性能,故优先选择方案二。

2 系统设计与FPGA实现

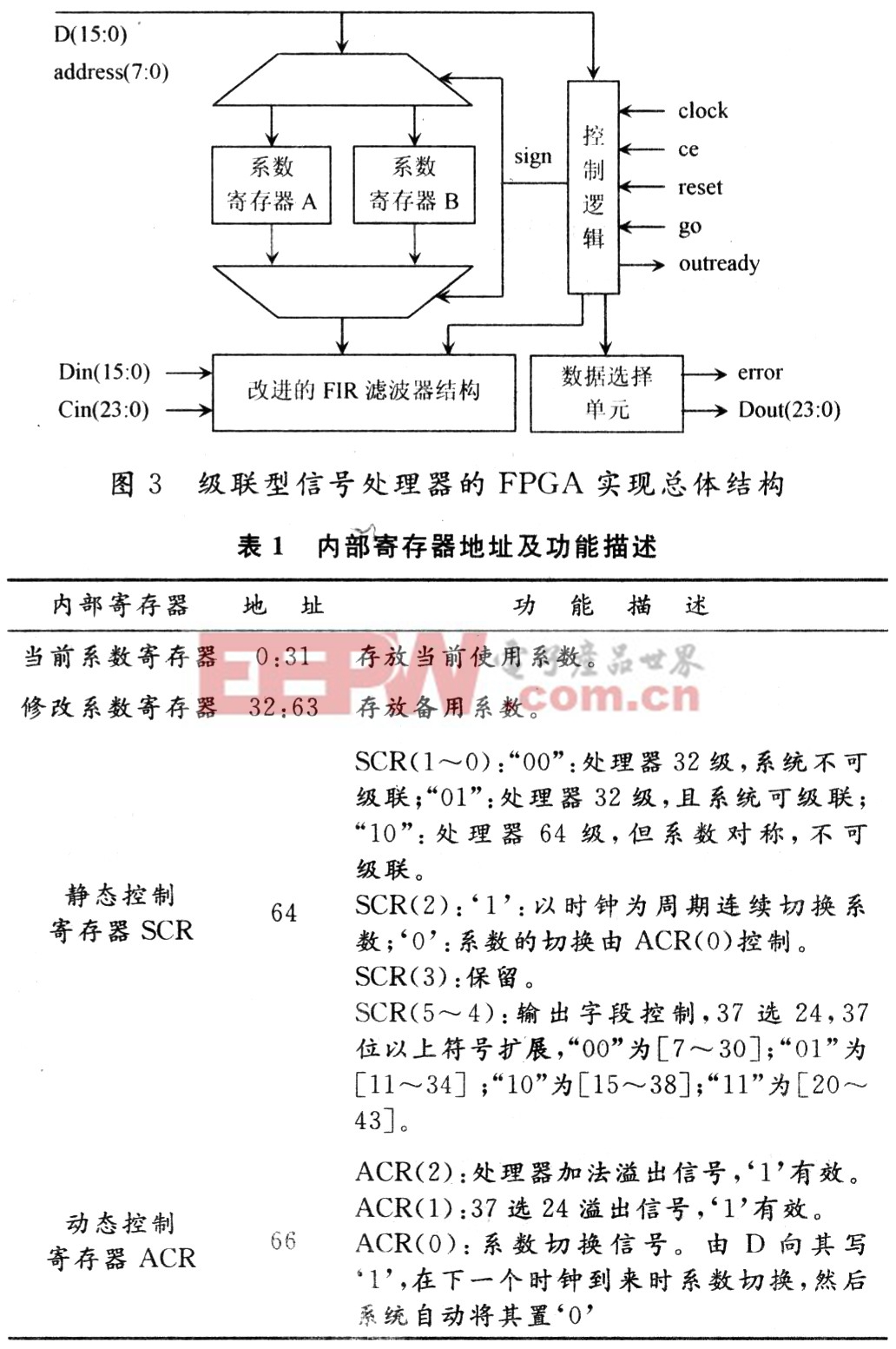

图2的FIR滤波器结构是高速、高精度的数字式横向滤波器结构,在数字信号处理应用中可作为功能块,完成高速离散傅里叶变换、卷积和相关,以及滤波功能。级联型信号处理器的设计正是基于此结构,其FPGA实现的总体结构如图3所示。

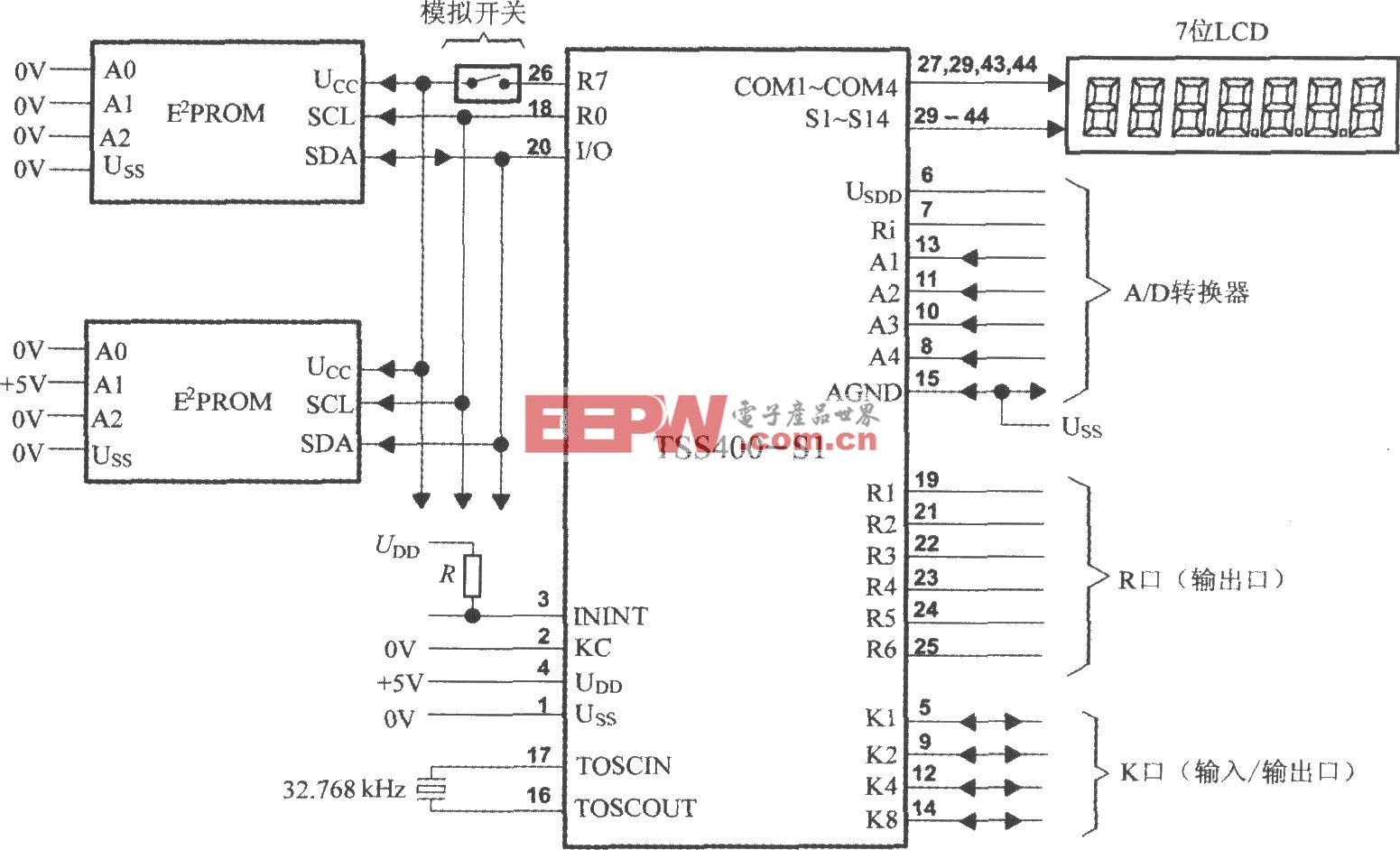

此级联型信号处理器的外部输入数据Din字长16位,系数字长16位,输入数据和系数均采用二进制补码方式。内部有A,B两组系数寄存器,一个存储当前系数,另一个存储修改系数,用户可通过数据线D在与系统时钟异步的情况下对系数进行修改,也可使A,B两组系数在系统工作的过程中相互“交换”。系统具有用户控制切换和系统自动切换两种系数切换方式。为了保持完整的数据精度,对于延时、乘法和相加链的中间结果是以满精度进行运算的,若N=2K,则系统的满精度为31+K位,考虑到单片使用时N级可扩展到2N级,所以应选用的满精度为32+K位,本系统采用32阶滤波器设计,故满精度为37位。在延时、乘法和相加链的输出端,设计一个可编程的桶形移位器(即数据选择单元),它可从四组24位数据字段[7~30],[11~34],[15~38]和[20~43]字段中任选一种,这四组字段从FIR滤波器输出的37位结果[0~36]中得到,所选的24位在输出前需进行舍入或符号扩展,至于如何选择,则根据实际应用而定。另外,本系统还为用户提供了系统复位(reset)、工作许可(go)、状态监测(error,out-ready)等常用握手信号。用户可以读写控制逻辑中的状态控制寄存器来切换当前系数,选择输出字段和设置系统工作模式(单片或级联,当系统课用于级联时,Cin为级联输入),其内部寄存器的详细描述见表1。

用户还可以通过数据线D、地址信号address、读写控制信号W、系统使能信号Ce、片选信号Cs等对系数寄存器A,B以及状态控制寄存器进行读写。

评论