通过在FPGA设计流程引入功率分析改善PCB的可靠性

器件的I/O消耗大量的功率,对于一个指定设计可以将其配置成串行或混合结构。由用户提供的信号(输入情况)或作为设计的输出(输出情况)的信号决定了混合I/O的状态。I/O转换速率定义了它们的状态。下列方程定义了输出的转换速率,用MHz表示。本文引用地址:http://www.eepw.com.cn/article/191979.htm

转换速率(MHz) = 1/2×fMAX×AF%

其它环境因素,如电路板的面积、散热片和气流都是计算动态和静态功耗时的要素。

管理功耗

现今最关键的设计要素之一是必须降低系统的功耗,特别是对于手持设备和电子产品而言。用户可以利用一些FPGA设计技术来有效地降低整个系统的功耗,包括:

1. 降低工作电压。

2. 在指定的封装温度限制范围内运作。

3. 使用优化的时钟频率,因为动态功率直接与工作频率成正比。设计者必须明确,如果设计的某部分可以以较低速率时钟控制,那将会降低功耗。

4. 减小设计在器件中的跨度,紧密放置的设计可使用较少的布线资源以降低功耗。

5. 可能的话,减小I/O的电压摆幅。

6. 可能的话,使用优化的编码。例如16位的二进制计数器平均只有12%的活性因子,7位的二进制计数器平均有28%的活性因子。另一方面,7位线性反馈移位寄存器的可以以50%活性因子转换,这会导致较大的功耗。每个时钟沿仅有一位改变的格雷码计数器所消耗的功率最少,同时活性因子将低于10%。

7. 利用以下方法尽可能减小工作温度:使用散热性能较好的封装,例如具有较低热阻抗的封装;在PCB上的器件周围放置散热片和散热层;采用更好的气流技术,如机械气流导管和风扇(系统风扇和器件风扇)。

典型的功率分析方案

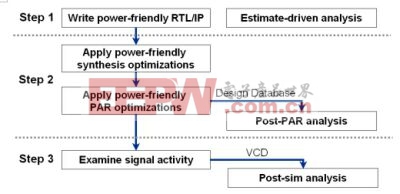

可以在FPGA设计流程的任何阶段用FPGA功率分析工具估算功耗。例如,可以在实际设计完成之前、或在布局布线后导入最终设计数据库时,用这个工具来估算功耗。当与映射后、布局后或者布线后的结果一起提供时,功率分析工具的精度得到提升。结合了功率分析的FPGA设计流程通常可提供重要的事件:驱动估计、后布局布线,以及后仿真。图2显示了该流程以及在功率的FPGA设计流程中的典型重要事件。

1.驱动估计:采用的资源和转换频率由手工输入。

2.Post-PAR:针对更加精确的模型导入后布局和布线资源。

3.后仿真:针对更加精确的活性因子和转换速率模型,导入由HDL仿真器产生的转换频率。

图2:面向FPGA功率分析的设计流程。

为适应提供给分析工具的不同模型数量,功率估计工具的运作可能是形式上的。在“驱动预计”模式下,分析引擎根据器件资源或者由用户提供的模板计算功耗。在对器件评估和进行“假设分析”时,这种模式最初是非常有用的。在该模式下,设计者提供频率、活性因子、电压参数和器件利用率。还需要提供工作条件,例如环境温度。利用先进的功率工具,设计者还可以选择诸如电路板尺寸、散热片和气流等。

评论