基于CPLD的CIS图像传感器驱动电路设计

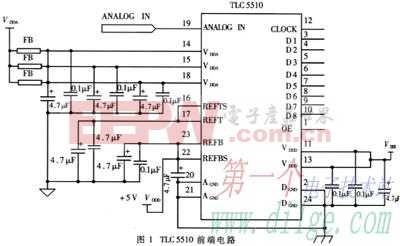

(3)A/D转换器的电路设计

由于灰度图像的灰阶通常为 256级,因此选用 8位的高速并行模数转换器 TLC5540,它的最高工作频率高达 40MHz,依靠 5V单电源工作,而且内部带有基准电路构成分压电路获得参考电压[1]。+5V

本文引用地址:http://www.eepw.com.cn/article/191968.htm

本文引用地址:http://www.eepw.com.cn/article/191968.htmTLC5540在其时钟信号的下降沿对输入模拟信号进行保持和采样,在 2.5个时钟周期后将转换的数据输出到内部总线上。当 TLC5540读选通信号 OE有效时,数据输出到外围管

脚上。 TLC5540的接口电路如图 3所示。

TLC5540的参考电压由精密基准电压源 TL431、电阻 R6和 R7构成的电路提供。 TLC5540的 CLK管脚和 OE管脚由 CPLD直接控制,分别为 AD_EN和 AD_CLK。当 CPLD产生的 AD_EN为下降沿时,CPLD使能 TLC5540的 OE脚将数据 AD[0..7]读取到 CPLD的内部寄存器中,实现信号由模拟到数字的转换过程。 3 软件设计

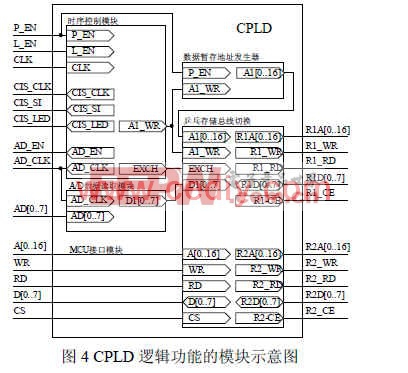

3.1 CPLD的逻辑功能模块设计

CPLD是 CIS控制模块的核心部件。根据 CPLD需要完成的任务,将 CPLD的逻辑功能划分为不同的模块,包括时序控制模块、 A/D数据读取模块、数据暂存地址发生器、乒乓存储的总线切换和 MPU接口模块等。CPLD逻辑功能的模块如图 4所示。

3.2时序控制模块

时序控制模块是 CPLD在外部时钟信号 CLK控制下,根据 MPU提供的 P_EN与 L_EN信号,产生 CIS的控制时序、A/D转换器的控制时序、数据暂存的读写信号。

(1)CIS传感器和 AD转换器的控制时序产生

根据 CIS传感器的控制时序特性, CPLD为 CIS传感器提供时钟信号 CIS_CLK、选通信号 CIS_SI和光源控制信号 CIS_LED等。当微处理器将 P_EN置为高电平时,CPLD处于初始化状态。当 P_EN为低电平后,CPLD处于准备阶段。此时,一旦微处理器给 L_EN管脚上产生一个脉冲信号,CPLD就随后自动产生 CIS_SI信号启动 CIS,同时 CPLD的内部计数器对外部 CLK进行计数。在根据计数值 CPLD产生 AD转换器的控制信号。这一时序电路的硬件描述如下,其中 CNT是一个 0到 647的计数器。

if P_EN ='1' then

CNT=0; AD_EN='1'; CIS_SI='0';

elsif (CLK 'event and CLK ='1') then

if L_EN ='1' then CNT=1;

elsif CNT=647 or CNT=0 then CNT=0;

else CNT=CNT+1; end if;

if CNT=2 then CIS_SI ='1';

else CIS_SI ='0';end if;

if CNT>=64 and CNT=640 then AD_EN='0';

else AD_EN='1'; end if; end if;

3.3 A/D数据读取模块

A/D数据读取模块将模数转换器的输出数据暂存在 CPLD内部寄存器中。在 A/D转换器的读使能信号有效,即 AD_EN为 0时, CPLD为 ADC产生时钟 AD_CLK。CPLD在 AD_CLK的下降沿将 ADC的转换结果暂存在寄存器 D1中,其硬件的描述如下。

if AD_CLK'EVENT and AD_CLK ='0' then D1(7 downto 0)=AD(7 downto 0); end if;

3.4数据暂存的地址发生器

CIS传感器是按照一个个像素逐次串行输出。因此必须将图像数据按照地址逐次增一的格式存储在存储器 IS61C1024中。其写信号 A1_WR是由 A/D转换器的读使能信号 AD_EN和外部时钟 CLK进行逻辑与得到的,其硬件描述如下。

A1_WR=AD_EN and CLK;

存储地址的产生是由一个 17位计数器 A1完成,当 P_EN=1时表示图像采集没有开始,地址计数器 A1初始化为0。当 P_EN=0时,在写信号 A1_WR的上升沿地址增 1,为下一个数据的存储提供地址。这一过程的硬件描述如下。

评论