SAW传感器后端信号处理电路的设计

在设计中,通过两位量程选择开关的控制,对时钟信号进行分频,可以得到1 s,100 ms,10 ms和1 ms四个不同的闸门开通时间。同时,计数部分采用六位十进制计数,于是可以得到0.1~100 MHz四个频率检测量程。

2.3 仿真及其测试

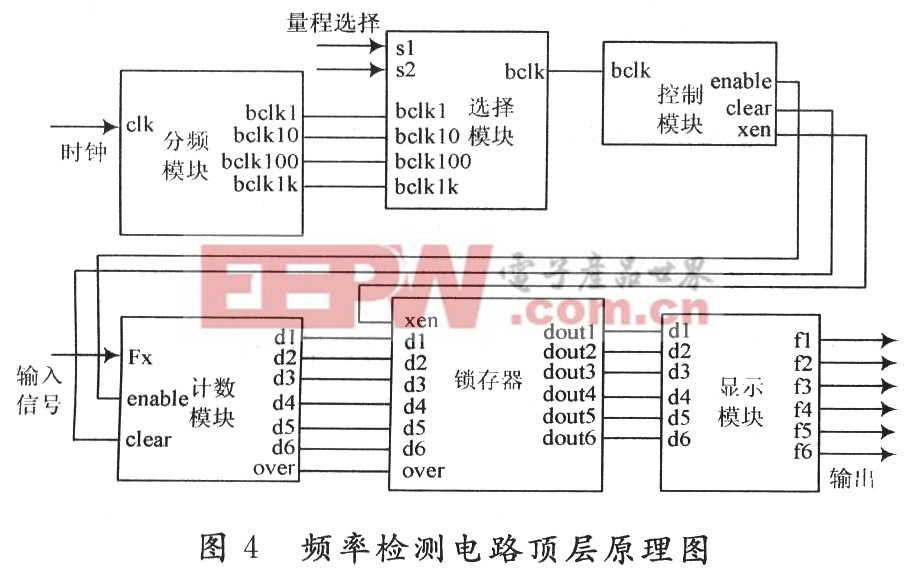

利用VHDL语言对电路的各个子模块编写相应的代码,并用EDA软件QuartusⅡ对源程序进行了编译、优化、逻辑综合,自动地将VHDL语言转换成门级电路,进而完成了对电路的分析、验证、自动布局布线、时序仿真、管脚锁定等各种工作。最终所设计的顶层电路如图4所示。该电路结构中,clk为系统的时钟信号;Fx为输入的检测信号;s1,s2为整个电路的量程选择控制输入端。通过s1, s2可以控制频率检测电路检测范围。

最后,采用了Altera DE2开发板,将设计的电路下载到硬件电路中,从而完成了对整个频率检测电路的设计工作,并利用函数发生器对电路进行了验证。在2 MHz左右的测试结果如表1所示。

3 结 语

本文设计了一种SAW传感器中的信号处理电路,对该电路中的频率检测部分,利用了FPGA技术,使频率检测的范围和精度满足了传感器的要求。通过对所设计电路的计算机仿真和实验,验证了设计的信号处理电路的可行性。

评论