分布式运算单元的原理及其实现方法

若将式(4)每个方括号之间的加法并行执行,即将每个DA查找表的输出采用并行的加法,就得到了全并行结构。现将式(4)中的某个方括号重写如下,并缩写为sum:本文引用地址:http://www.eepw.com.cn/article/191941.htm

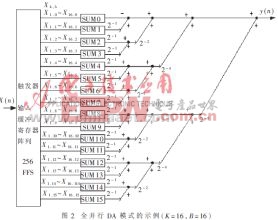

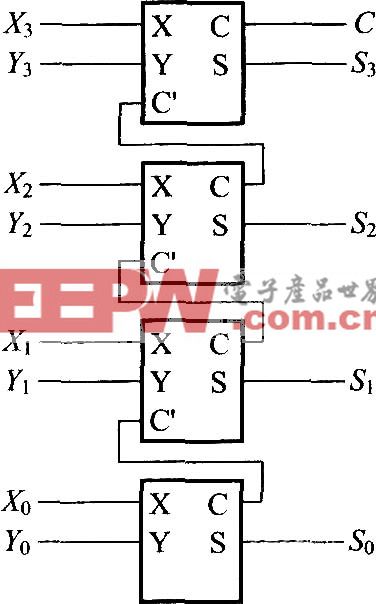

利用式(6),可以得到一种直观的树形阵列,如图2所示。

图2中,首先要建立一个K×B位的寄存器阵列,将其输出进行排列,用所有K个输入数据的相同位,对 DA查找表寻址,从图中可以看出,当B=16时,输入到输出所需的路径最长,该路径为关键路径,影响着电路处理的速度,在进行设计时应该注意到这点,所以应该采用流水线设计方法[1],并进行适当的约束,其数据率可以达到50MHz。图中的15个节点代表着15个并行的加法器,中间过程的数据宽度既可以保持双精度(B+C)位数据(C是常数Ak的宽度),也可以采用截尾的办法得到单精度B位数据,可根据系统所要求的精度确定。

2.2 全串行实现方法

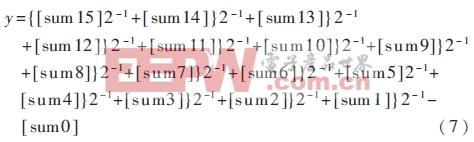

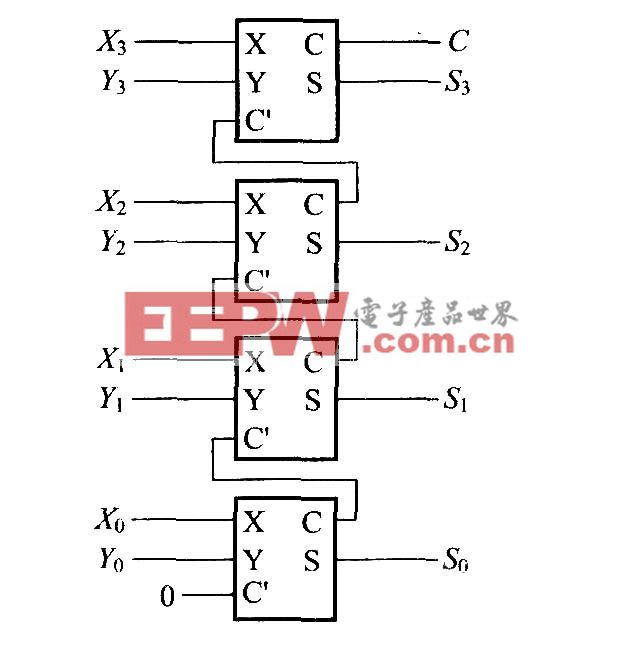

当系统对速度的要求不是很高的时候,可以用全串行设计方法,即一个DA查找表,一个并行的加法器以及简单少量的寄存器就可达到目的,这样能够节省大量的FPGA资源。同样,设K=16,B=16,将式(4)改写如下形式:

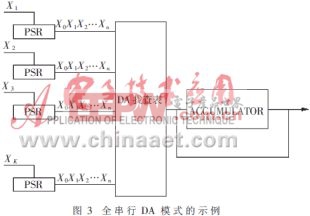

为了实现式(7),先从最低位开始,用所有K个输入变量的最底位对DA查找表进行寻址,得到了[sum15],将[sum15]右移一位即将 [sum15]乘2-1后,放到寄存器中,设为[tem15];同时,K个输入变量的次低位已经开始对DA查找表寻址得到[sum14],右移一位后,与 [tem15]相加,重复这样的过程,直至得到[sum0],并用前面得到的累加结果减去[sum0]。要实现上述过程,需要K个长度为B的串并行转换移位寄存器、一个容量为2K×C的DA查找表和一个累加器。该全串行电路的数据率为输入数据抽样频率的1/B,即完成一次运算需要B个时钟周期。由此可以得到全串行DA模式,如图3所示。

2.3 串并行相结合实现方法

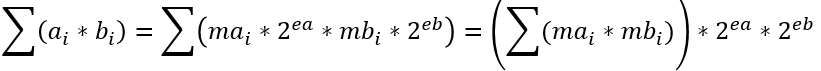

以上介绍的全串行方式是每个时钟周期对所有K个变量的一位进行串行处理,全并行方式是每个时钟周期对所有K个变量的所有B位进行并行处理;这两种方法是针对速度优化和资源优化设计的两种极限情况。在有些情况下,我们可以对这两种情况进行折中考虑,获得最佳资源利用和系统速度。我们可以从每个时钟周期对K个变量的两位进行处理开始着手,回顾一下式(5),并将该式改写如下:

完成该式功能的功能框图如图4a所示。

评论