安全芯片中密码算法的多IP核集成方法

⑥执行指令

MOV INSTRUCT,#00H

关闭SHA1协处理器,完成SHA1调用。

对TDES及RSA的功能调用类似于SHA1,仅在指令配置时稍有不同。TDES增加了密钥生成过程的指令配置与完成信号判断,RSA增加了对模长与模幂的参数配置。由上可知,与方法二相比较,IP桥接技术在调用实现IP核功能时,需要增加的仅为一条IP选择参数配置指令。 本文引用地址:http://www.eepw.com.cn/article/191926.htm

3 测试与仿真

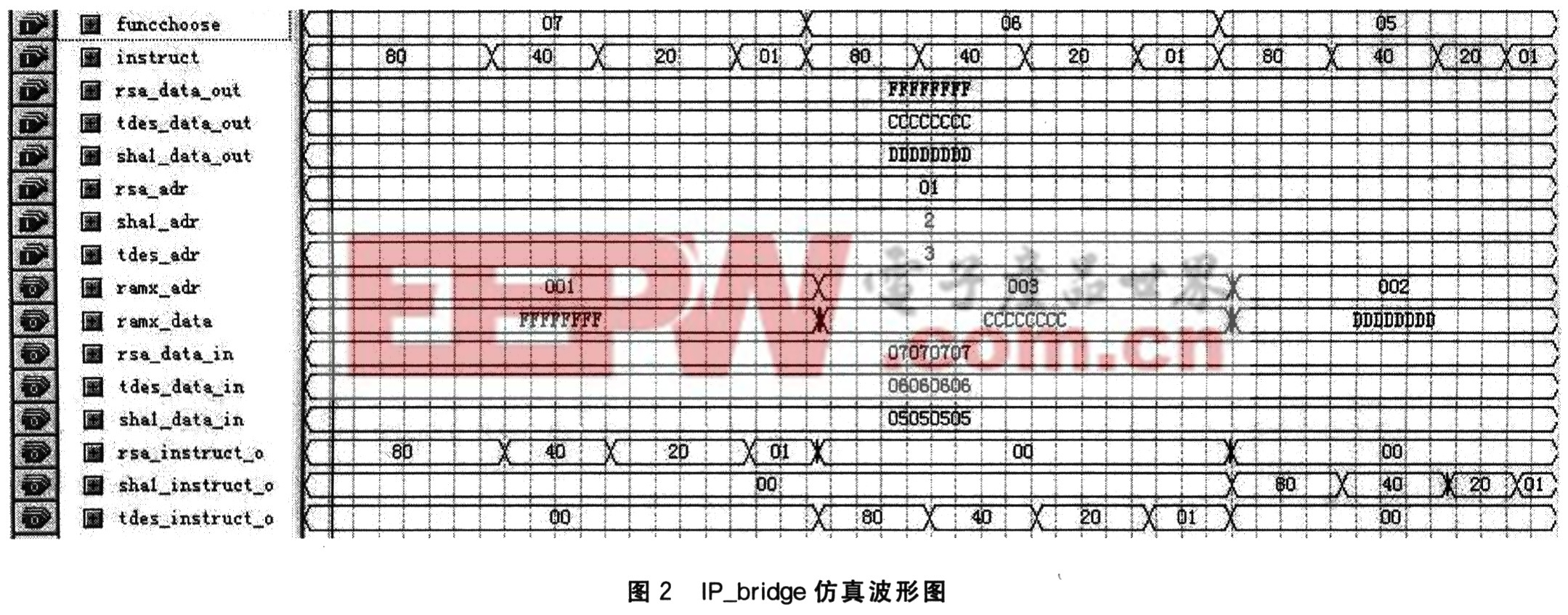

本文采用软件仿真与FPGA下载测试两种手段,对2.2中的设计进行了功能正确性验证。图2给出了该设计中IP_bridge在quartus II 5.0下的仿真波形图。

在图2中,FUNCCHOOSE为系统功能区的IP选择参数输入,INSTRUCT为IP控制指令。当IP选择参数值为07H、06H、05H时,对应的选定IP为RSA、TDES、SHA1。以选定SHA1为例,当IP选择参数为05H时,IP_bridge模块重构asis_ramx为SHA1专用数据处理区,且此时SHA1控制指令shal_instruct_o被配置为当前IN-STRUCT值,完成对SHA1的接口配置;当IP选择参数为 06H、07H时,IP_bridge置SHA1控制指令shal_in-struct_o为00H,使SHA1协处理器处于休眠状态。对 IP_bridge仿真波形图的分析表明,其逻辑功能正确。由于在初次FPGA下载测试时发现,允许IP_bridge对IP核进行时钟配置会导致协处理器功能不稳定,因而取消了IP_bridge的IP核时钟配置功能。除此以外,其余部分均满足本文2.1中的功能要求。

为进一步验证设计的正确性,本文选用Altera公司Cyclone II系列EP2C35F672C6器件,对其进行了FPGA下载测试。在初次测试时发现,各IP核虽然可以完成功能调用,但执行结果不稳定,测试结果的最后5~10字节与标准测试对的结果不符。经分析发现,导致IP核功能错误的原因为IP_bridge在对时钟进行配置时,会产生时钟延迟。因此,取消了 IP_bridge的时钟配置功能,在Qu-artus II 5.0下进行编译仿真与综合下载,再次进行FPGA下载测试。测试结果显示,各IP核功能均正确无误。采用选定器件,IP_bridge逻辑资源消耗为 200 LE,最大路径延迟为16.838 ns。

结 语

本文在总结多IP核集成设计方法的基础上,提出了一种IP桥接技术,用于实现多IP核集成;并以其为指导,基于一个8位SoC系统,具体实现了三个IP核集成。功能仿真与FPGA测试表明该技术具备实际可行性,且相比较于现有多IP核集成方法,IP桥接技术具备可有效提高片内资源利用率,降低系统功耗与开发成本等优势;其缺点在于,当不同IP核的数据接口不一致时,IP_bridge的逻辑设计会比较复杂,且不能实现对IP核的变频时钟配置。初步分析表明,通过修改IP核的双端口存储区数据写入环节,延长数据写入完成至done信号有效这一时间段,可解决这一问题。方法的有效性检测与具体实现,是笔者下一步工作的重点研究内容。

评论