基于FPGA的改进型分组交织器的设计与实现

2.4 读写使能控制设计

考虑到双端口RAM对其内部同一单元地址不能同时进行读写操作,因此,整个交织器设计需用读写使能控制电路用来对双端口RAM的地址读写进行控制,并同时决定读写发生器何时开始工作。由于双端口RAM的读、写实现都是从零地址开始的,因而RAM内的每个存储单元的读操作都应在写操作之后,从而保证每个读出数据的有效性。

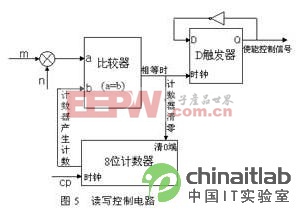

读写使能控制电路如图5所示,读写控制电路采用类似于分频器原理[4]的工作方式,电路主要由计数器、比较器和D触发器来实现:计数器与n m比较的结果作为D触发器的时钟脉冲信号,当计数器的计数值等于n m时,触发器的输出状态进行一次反转,即相当于构成了一个n m的分频器电路。触发器的输出结果分成两路:一路送到双端口RAM的写地址使能端;另一路经过反相后送给读地址使能端。这样便可以使存储器RAM在“n m”的地址空间范围内交替进行“读/写”数据的操作。

读写使能控制电路

2.5 设计中的遇到的问题及解决办法

交织器的设计中包含的运算有相乘和相加,相乘会造成字长的变化。这便会带来数据位数匹配的问题,下面我们以读地址电路(图4)为例给出解决办法:

进入乘法器的两路数据均为8位,经过乘法运算后,数据位数会增加到16位,同时需要与来自计数器Ⅱ的8位数据进行加法运算。通常情况下多采取舍入或截尾的方法,即将16位数据的高8位字节舍去,这种方法的不足是当m、n的乘积大于256(11111111H)时,数据的高8位不全为0,舍去会带来输出结果的错误,因而可能造成交织器输出码字的错误。因此,可采用“补位”的办法,将输入加法器的8位数据补成16位(在8位数据前补8位0),以增长位宽从而达到数位匹配的目的。

3 QuartusⅡ仿真结果及分析

交织器的仿真波形如图6所示(其中“clk”为驱动时钟,“rden”、“wren”为读、写使能,“data”、“result”为输入、输出双端口RAM的数据序列):

Quartus

从QuartusⅡ波形仿真结果看到当交织矩阵的m,n值为5和3时,双口RAM的输出数据为“0、5、10、1、6…”;当m,n调整为8和 6后,双口RAM的输出为“0、8、16、24…”。可以看出,在任意选取不同的m值和n值后,交织器能够根据分组交织的原理将输入RAM的数据字或比特位流进行交织,输出所需的数据序列,达到了交织矩阵深度和宽度可控的目的。

4 小结

本文介绍了可针对不同交织需要的改进型分组交织器FPGA设计,该交织器的主要特点是可根据信道中突发误码的长度、出现的频率以及纠错码的约束长度、纠错能力设定合适的交织深度和宽度(m,n),需要指出的是,m,n选得越大,信道编码的约束长度越大,从而对付信道中长突发差错的能力也就越强,但m,n选得越大,也就需要越大的存储空间,同时会引入更长的延时,所以应根据数字通信系统的实际情况选择合适的m值和n值。

本文作者创新点:对传统分组交织器进行了改进,实现了分组交织器的交织矩阵深度和宽度可控,能够很好的满足不同数据帧传输的要求,具有更好的抗信道突发错误的能力。

评论