基于FPGA的改进型分组交织器的设计与实现

在整个循环过程中,读地址变量add不断输出“乱序”的交织地址add=j n+i,以达到设计的要求。

通过上述分析可以看出,算法中运用了加法、乘法、比较、计数等算术逻辑运算,则地址生成的FPGA设计过程中,需要运用加法器,乘法器,比较器,计数器等器件以实现相应功能。在设计过程中,这些器件采用由QuartusⅡ软件为设计人员提供的参数化宏单元模块LPM(library of parameterized modules),使用它不仅可以简化电路复杂度,而且大大提高了设计速度。

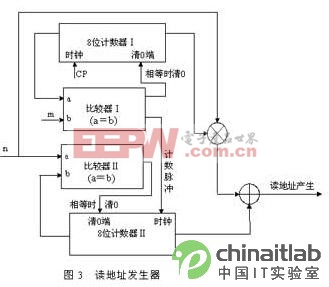

2.2.2 读地址序列产生器设计

读地址是整个交织器设计部分的关键,采用“乱序读出”的方式。电路设计主要由加法、乘法器,计数器和比较器模块构成,其地址序列产生流程在算法分析中已作过详细说明,这里只作简单介绍:计数器Ⅰ相当于变量j,首先在时间脉冲cp的驱动下从初始状态“00000000”开始递增计数,当等于设定交织深度m时,产生一个时钟脉冲信号来驱动计数器Ⅱ,此时计数器Ⅱ的计数加一,同时与另一设定数据n进行比较,当相等时计数器Ⅰ、Ⅱ同时清0,重新开始计数。

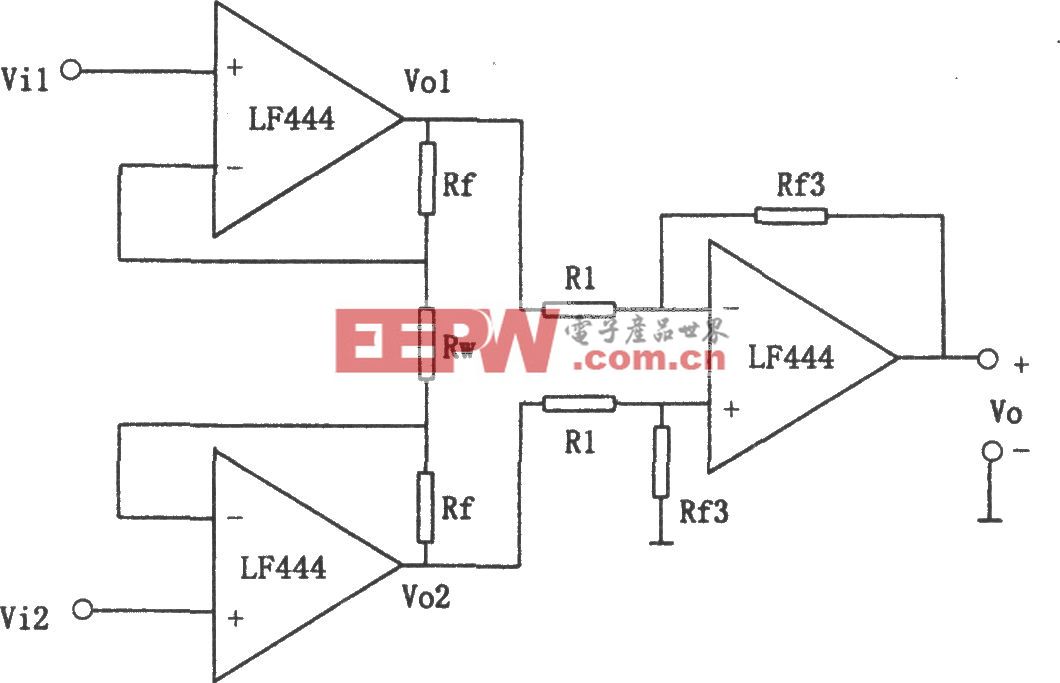

读地址序列产生器

读地址产生结果由数据n与计数器Ⅰ每次的输出数据相乘,再与计数器Ⅱ的计数数据相加而得到。产生的序列依次为:0,n,2n,…,(m-1)n,1,n+1,2n+1,…,(m-1)n+1,2,…,mn-1.

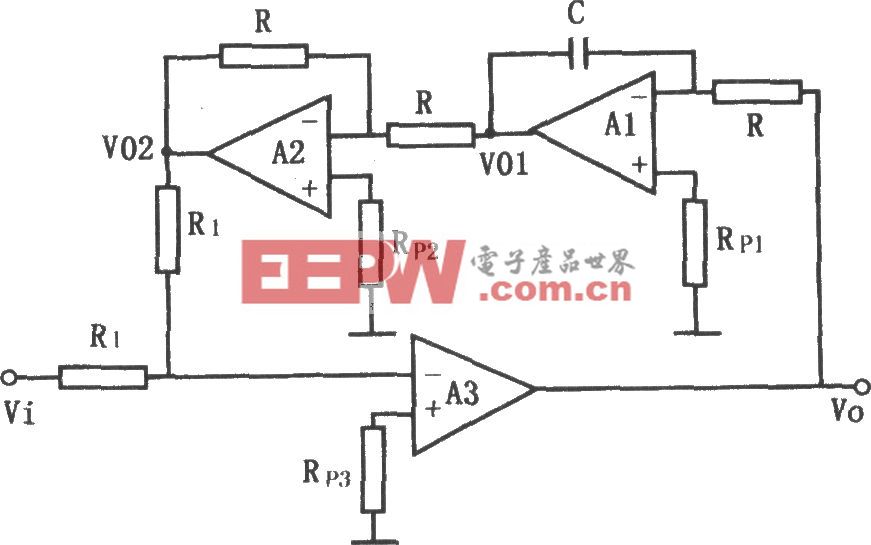

2.3 写地址序列产生器设计

交织器采用“顺序写入”的写地址方式,即产生“0,1,2 …,mn-1”的顺序地址序列。因此写地址序列产生器的实现可由乘法器,比较器和计数器等宏单元模块构成(如图4所示),写地址具体产生说明如下:

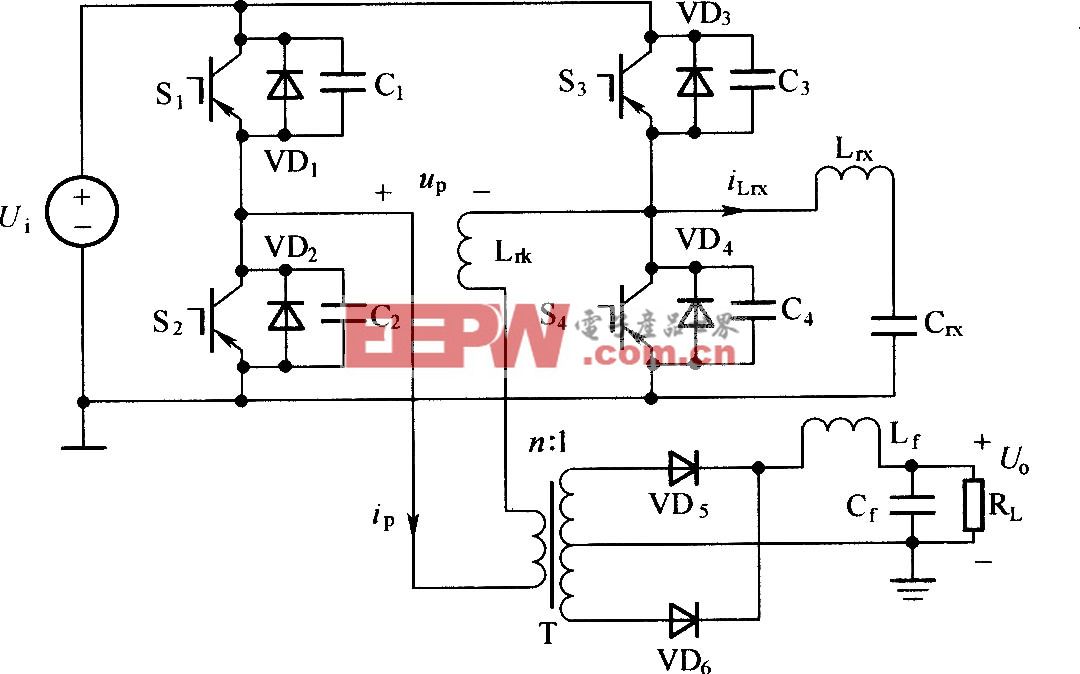

写地址序列产生器

首先8位计数器在时钟脉冲cp的驱动下由初始状态“00000000”开始递增计数,产生的计数数据分成两路:一路送到双端口RAM的写地址端,作为交织器的写地址产生信号;另一路则送到比较器的一个输入端,同乘法器输出的结果进行比较:当计数器累计计数值小于乘法器计算结果时,计数器继续累加计数;而当计数值等于乘法器的计算结果时,比较器产生中断控制信号使得计数器清0,并重新开始计数。

评论